# PRESENTATIONS AND WHITEPAPERS

**MEETING 1**

APRIL 7-8, 2009 SANTA FE, NEW MEXICO

**MEETING 2**

JUNE 28-29, 2009 PARIS, FRANCE

### **MEETING 1**

### **PRESENTATIONS**

### APRIL 7-8, 2009 SANTA FE, NEW MEXICO

#### **Improving HPC Software: Welcome**

Pete Beckman (Argonne National Laboratory/University of Chicago) and Jack Dongarra (University of Tennessee/Oak Ridge National Laboratory)

### e-Infrastructure in FP7: HPC related aspects

Catherine Riviére, GENCI, France

### Development of an Over Petascale Computer in Japan

Satoshi Matsuoka, GSIC Center, Tokyo Institute of Technology/National Institute of Informatics

### **International Exascale Software Program**

Abani Patra, NSF Office of Cyberinfrastructure

#### Improving HPC Software: Overview

Pete Beckman (Argonne National Laboratory/University of Chicago) and Jack Dongarra (University of Tennessee/Oak Ridge National Laboratory)

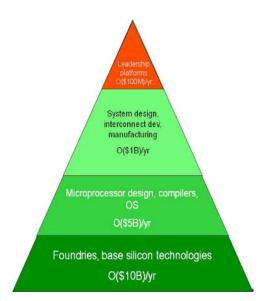

## Thou Shalt Specialize or Commoditize? The Japanese Situation Towards Peta and Exascale

Satoshi Matsuoka, GSIC Center, Tokyo Institute of Technology/National Institute of Informatics

# Technology and Architectures for Future Large-Scale Computing Systems

Rick Stevens, Argonne National Laboratory and University of Chicago.

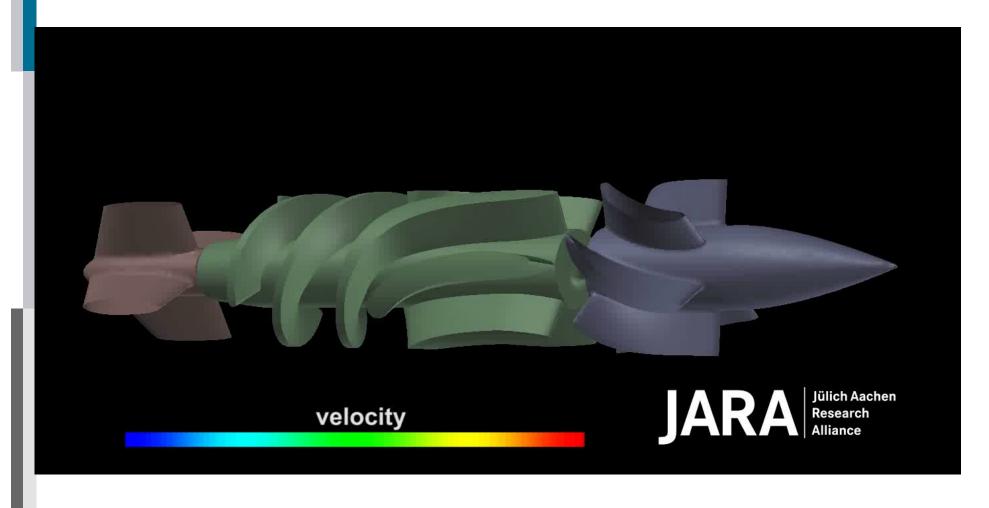

# Computational Science and HPC Software-Development in Europe

Thomas Lippert and Bernd Mohr, Forschungszentrum Jülich, JSC and Gauss Centre for Supercomputing e.V.

## Slides from the panel:Software Barriers to HPC, Today and Tomorrow

Panel participants: Al Gara, Jean-Yves Berthou, Mitsuhisa Sato, Peggy Williams, Vivek Sarkar, Ann Trefethen

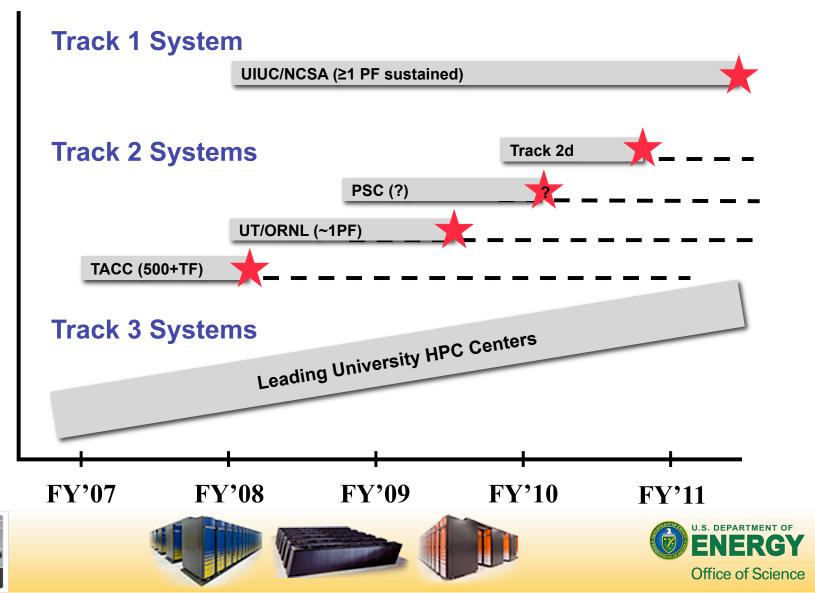

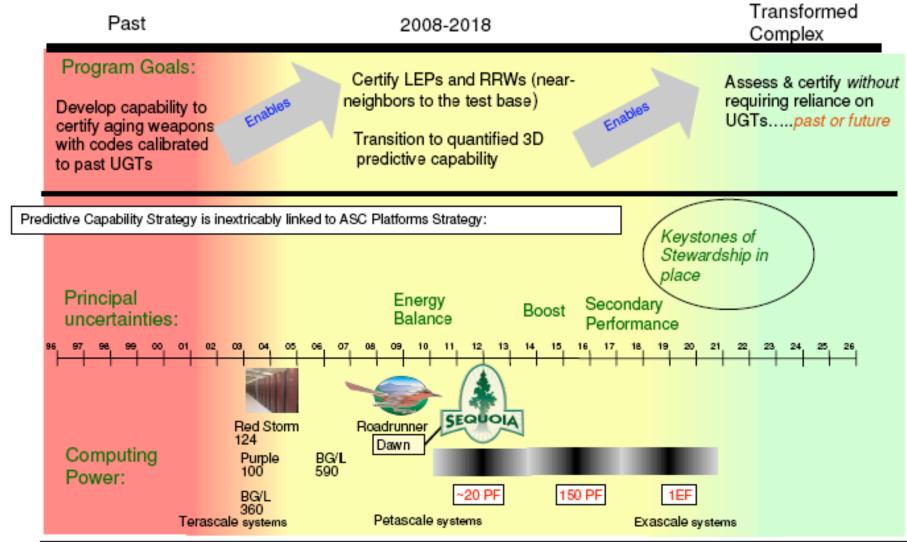

### Science Drivers, Current HPC Software Development, and Platform Deployment Plans

**for the USA** Horst Simon, Lawrence Berkeley National Laboratory and UC Berkeley

### **MEETING 1**

### **WHITEPAPERS**

### APRIL 7-8, 2009 SANTA FE, NEW MEXICO

### **Musings on the Path Toward Exascale**

Robert Lucas - ISI/USC

#### **BSC Vision Towards Exascale**

Mateo Valero, BSC

# Software Challenges of Extreme Scale Computing

Michael Heroux - Sandia National Laboratory

#### **Software and Exascale Computing**

Bill Camp - Intel Corporation

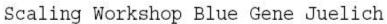

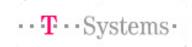

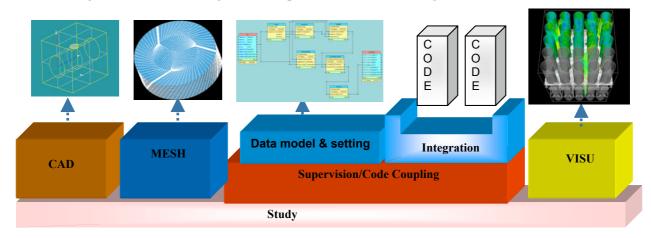

## Application Analysis and Porting in the PRACE Project

Peter Michielse - Netherlands National Computing Facilities Foundation (NCF)

# The Application Perspective - Seeking Productivity and Performance

David Barkai - Intel Corporation

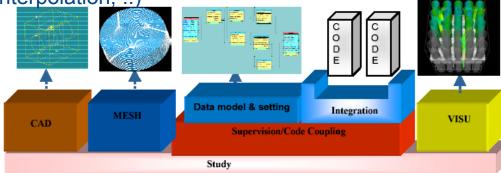

### **EDF** white paper

J.Y. Berthou and J.F. Hamelin - EDF R&D

#### The Biggest Need: A New Model of Computation

Thomas Sterling - Louisiana State University

#### **NSF IESP Whitepaper**

Abani Patra, Rob Pennington, Ed Seidel - Office of Cyberinfrastructure, National Science Foundation

#### A Proposal for a Capability Centers Consortium

Bill Gropp, Mark Snir - NCSA and the University of Illinois at Urbana-Champaign

#### **Slouching Towards Exascale**

Rusty Lusk, Argonne National Laboratory

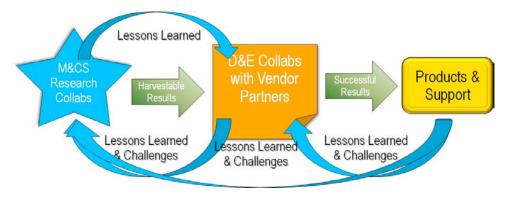

### A Collaboration and Commercialization Model for Exascale Software Research

Mark Seager and Brent Gorda, Lawrence Livermore National Laboratory

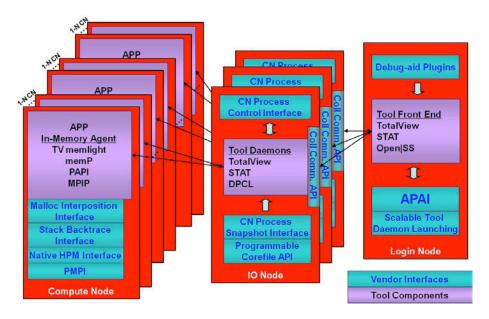

### The Case for A Hierarchal System Model for Linux Clusters

Mark Seager and Brent Gorda, Lawrence Livermore National Laboratory

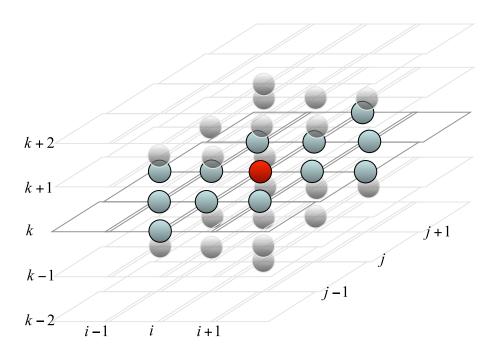

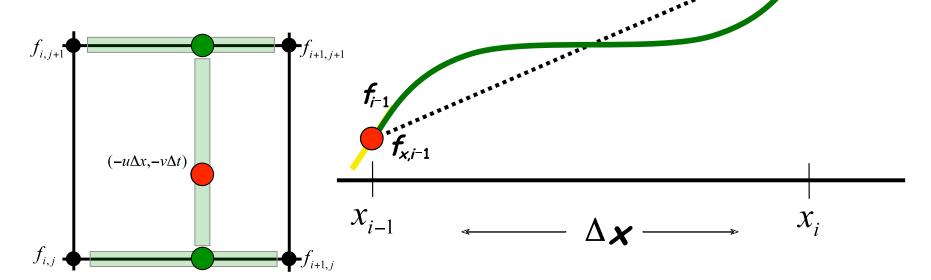

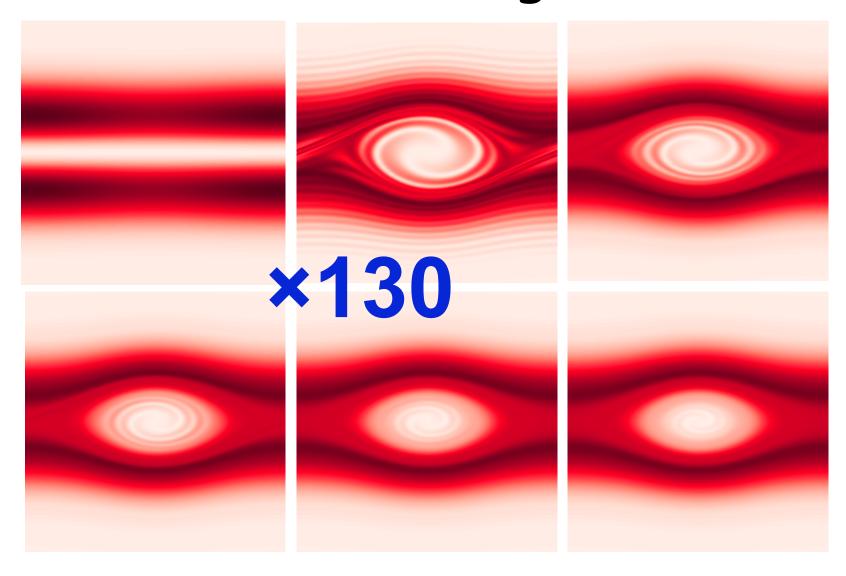

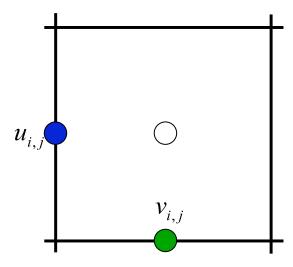

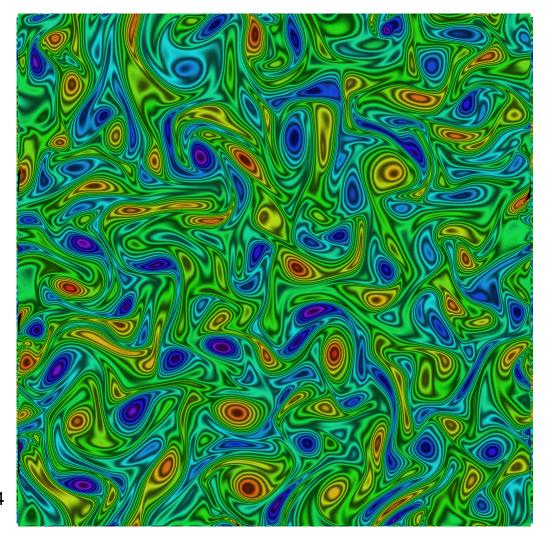

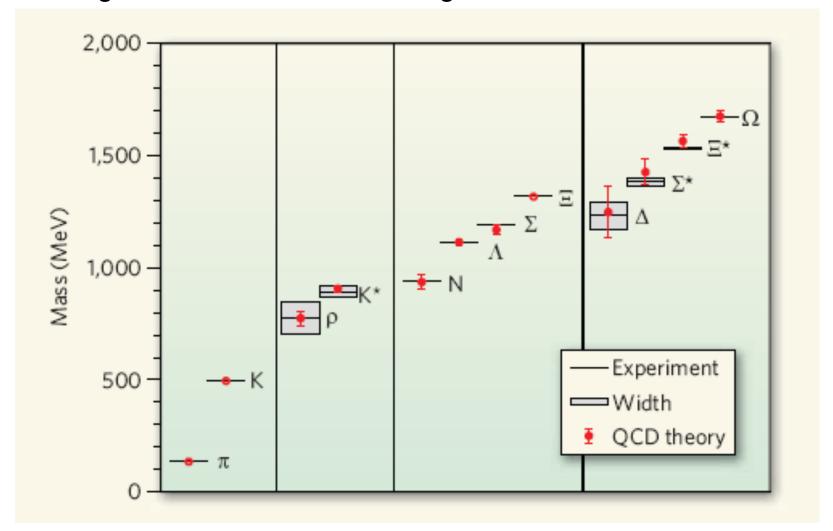

### PDE-based applications and solvers at extreme scale

David Keyes, Columbia University & SciDAC TOPS project

# Developing a high performance computing/numerical analysis roadmap

Ann Trefethen, Nick Higham, Ian Duff, and Peter Coveney

# PRESENTATIONS AND WHITEPAPERS

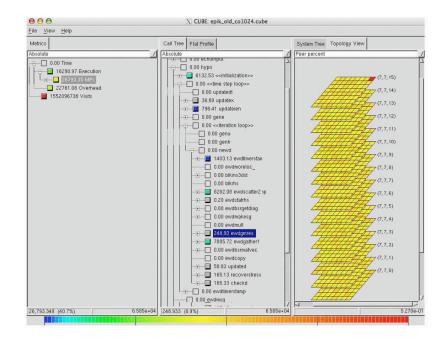

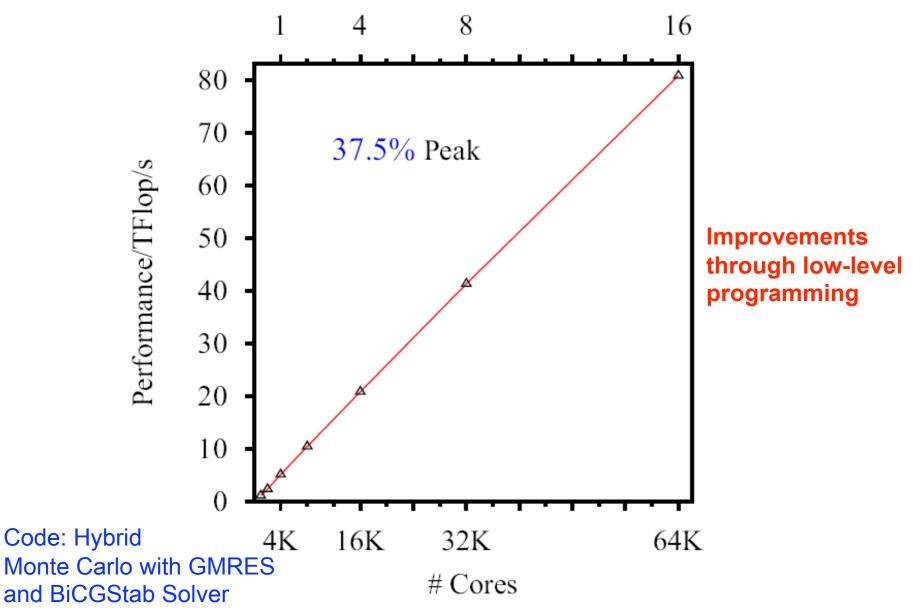

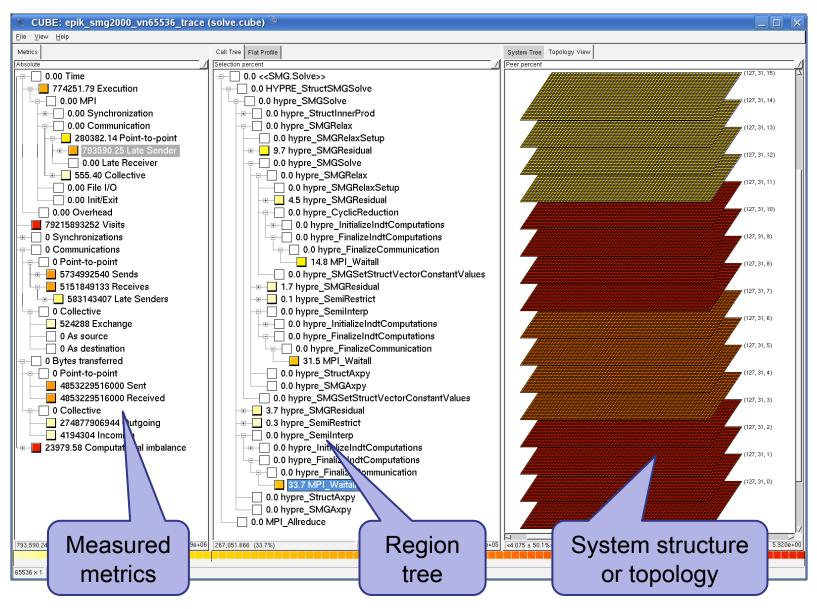

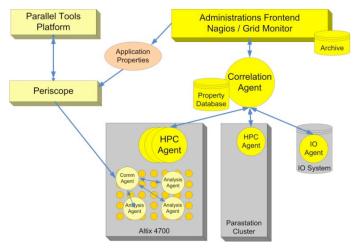

#### Performance at Exascale

Bernd Mohr (Jülich Supercomputing Centre) and Matthias S. Mueller (Wolfgang E. Nagel Center for Information Services and HPC)

#### **Resource Management**

Barney McCabe (ORNL) and Hugo Falter (ParTec)

#### **Programmability Issues**

Vivek Sarkar (Rice U.), Jesus Labarta (UPC), Mitsuhisa Sato (U. of Tsukuba), Barbara Chapman (U. of Houston)

### **Models of Computation – Enabling Exascale**

Thomas Sterling, Louisiana State University

### Major Computer Science Challenges at Exascale

Al Geist (ORNL) and Robert Lucas (ISI)

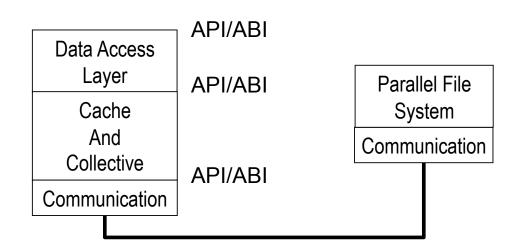

#### Towards Exascale File I/O

Yutaka Ishikawa, University of Tokyo

#### **Co-design of Architectures and Algorithms**

Al Geist (ORNL) and Sudip Dosanjh (SNL)

### IESP Exascale Challenge: Resilience and Fault Tolerance

Al Geist (ORNL) and Franck Cappello (INRIA)

### **Consistent Application Performance at Exascale**

William Kramer and David Skinner

# An Exascale Approach to Software and Hardware Design

William Kramer and David Skinner

Improving HPC Software

# **IESP** the Need

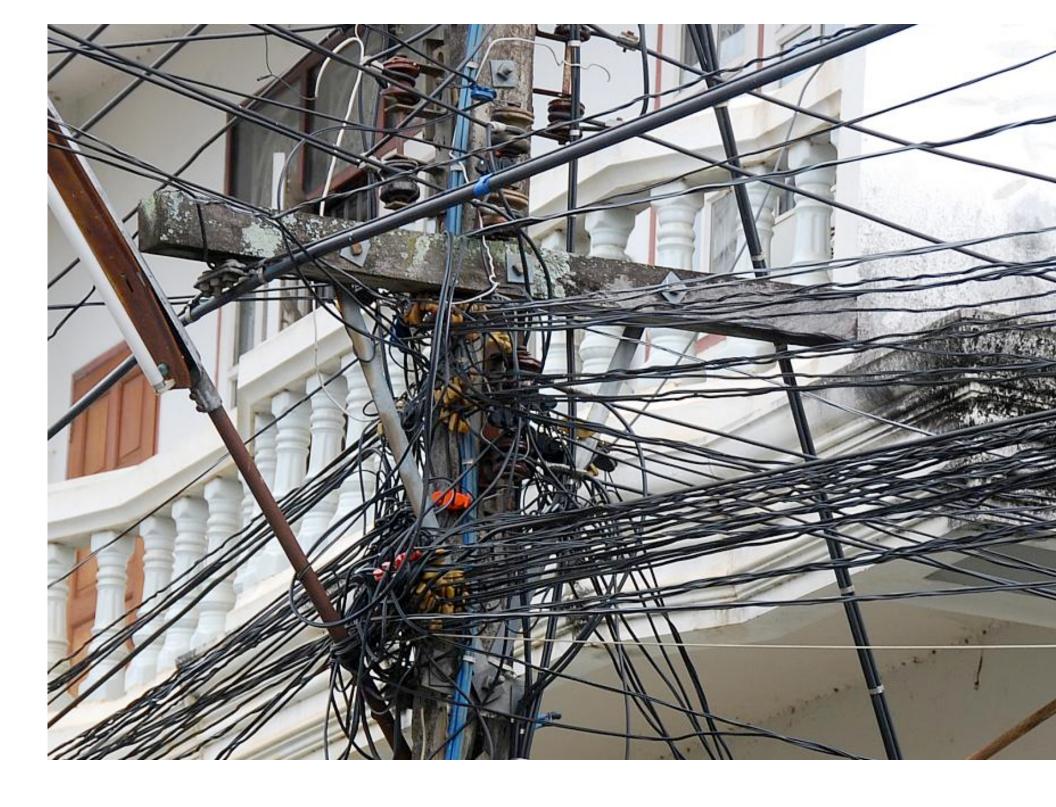

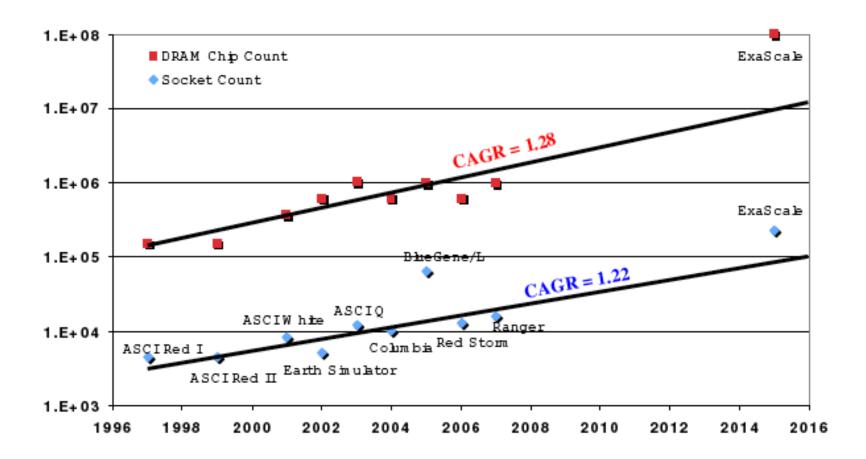

- The largest scale systems are becoming more complex, with designs supported by large consortium

- The software community has responded slowly

- Significant architectural changes arriving

- Software must dramatically change

- Our ad hoc community coordinates poorly, both with other software components and with the vendors

- Computational science could achieve more with improved development and coordination

# Where We Are Today:

## We are not prepared for the changes coming

- Hardware features are uncoordinated with software development

- (power mgmt, multicore tools, math libraries, advanced memory models, etc)

- Only basic acceptance test software is delivered with platform

- □ UPC, HPCToolkit, Optimized libraries, PAPI, can be YEARS late

- Vendors often "snapshot" key Open Source components and then deliver a stale code branch

- □ Counterexample: A model that works MPICH for BG/P

- Community codes unprepared for sea change in architectures

- Coordination via SOW/contract is poor and only involves 2 parties

- No global evaluation of key missing components

# The IESP Workshops:

- Goal: Improve the world's simulation and modeling capability by improving the coordination and development of the HPC software environment.

- Build a plan for how the international community can join together to improve software available for high-end systems over the next 2 to 10 years.

- The DOE (SC, NNSA), NSF, and EU have committed their support for the workshops.

- This is the first workshop in the series of three.

# International Community Effort

- We believe this needs to be international collaboration for various reasons including:

- The scale of investment

- The need for international input on requirements

- Europeans, Asians, and others are working on their own software that should be part of a larger vision for HPC.

- The process must be totally open

### **Executive Committee:**

Co-Chair: Jack Dongarra, Univ, of Tennessee / ORNL, US

Co-Chair: Pete Beckman, Argonne National Laboratory, US

Franck Cappello, INRIA, FR

Thomas Lippert, Jülich Supercomputing Centre, DE

Satoshi Matsuoka, Tokyo Institute of Technology, JP

Paul Messina, Argonne National Laboratory, US

# A Plan Could Include:

- Work with vendors to create the HPC equivalent to the ITRS (Int'l Tech Roadmap for Semiconductors)

- Get community working on software before machine becomes available

- Community proposed unified roadmap for exascale software

- Identify missing components for future architectures and a plan to address them

- Develop models for working more closely with vendors

- (support, acceptance tests, target features)

- Identify key application areas to drive development

- Community software development models

- Funding and organizational models

# Achievable Outcomes

- Improve the capability of computational science

- Build and strengthen international collaborations and leadership; deliver more capable, productive HPC systems

- Build and improve R&D program developing new programming models and tools addressing extreme scale

- Open source HPC development guided by roadmap with better coordination and fewer missing components

- Joint programs in education and training for the next generation of computational scientists.

- Vendor engagement and coordination for more capable software supporting exascale science

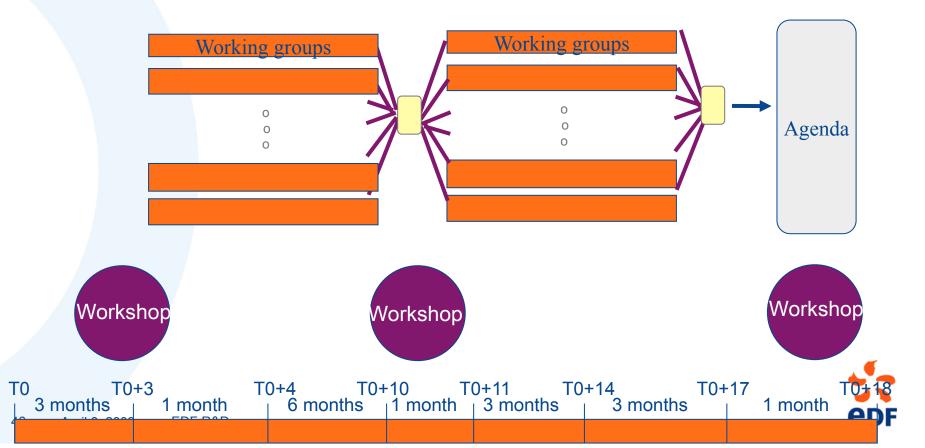

# Workshops and Report

- 3 workshops over the next year

- □ 1: Santa Fe, April 7-8

- □ 2: Paris France, June 28-29

- 3: Japan in the early Fall

- Broad engagement by the community

- Initial reports in summer 2009

- Final report for first year at SC09

- Planning for IMMEDIATE payoff

- Could begin ramping up next year

# www.exascale.org

Home Meetings Documents Community Help

### **Main Page**

Page

Discussion

View source

History

The mission of the **International Exascale Software Project (IESP)** is to lay the foundation for exascale computing by mobilizing the global open source software community to combine and coordinate their collective efforts far more efficiently and effectively than ever before. The IESP will hold a series of three workshops to organize and structure this community wide effort. The first, invitation-only workshop will occur on April 7th and 8th in

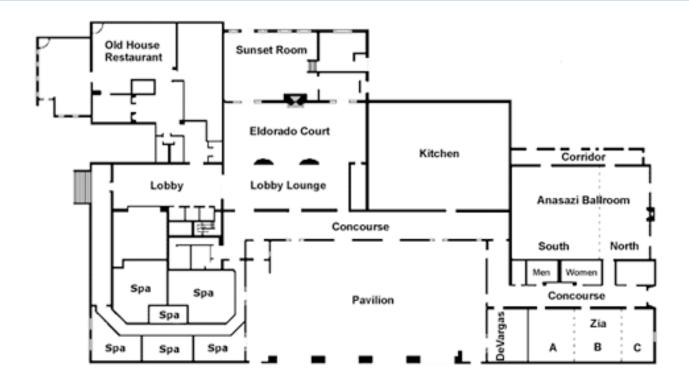

### Workshop Information

Workshop Location

Workshop Agenda (draft)

Executive Committee

Organizing Committee

Background Material

Sante Fe, New Mexico, US, with people arriving in time for a reception on April 6th. Attendees will include members from industry, academia, and government, with expertise in a range of critical areas.

Goals for the first meeting include the following:

- Assess the short-term, medium-term and long-term needs of applications for peta/exascale systems

- Explore how laboratories, universities, and vendors can work together on coordinated HPC software

- Understand existing R&D plans addressing new programming models and tools addressing extreme scale, multicore, heterogeneity and performance

- Start development of a roadmap for software on extreme-scale systems

**Attendance at the workshop is by invitation only.** Additional details on registration will be coming soon.

# **IESP**

- Plan to build an international partnership that joins together industry, the HPC community, and production HPC facilities in a collective effort to design, coordinate, and integrate software for leadershipclass machines.

- Build an international plan for developing the next generation open source software for scientific highperformance computing

# Engagement in the Following Activities

- Build international collaborations in the areas of high-performance computing software and applications.

- Development of open source systems software, I/O, data management, visualization, and libraries of all forms targeting tera/peta/exascale computing platforms,

- R&D of new programming models and tools addressing extreme scale, multicore, heterogeneity and performance,

- Cooperation in large-scale systems deployments for attacking global challenges,

- Joint programs in education and training for the next generation of computational scientists.

- Vendor engagement to coordinate on how to deal with anticipated scale.

# Goals for this the workshop include

- Assess the short-term, medium-term and long-term needs of applications for peta/exascale systems

- Explore how laboratories, universities, and vendors can work together on coordinated HPC software

- Understand existing R&D plans addressing new programming models and tools addressing extreme scale, multicore, heterogeneity and performance

- Start development of a roadmap for software on extreme-scale systems

# **Topics**

- Purpose of the workshop series, desired outcome (international Research, Development, & Deployment efforts for open source system software and tools for exascale computers)

- Identify key technical areas on which to focus, e.g., file systems, message-passing and multi-threading sw, fundamental numerical sw, system management tools, debuggers, ...

- Begin to identify which groups would like to tackle what areas and which funding sources might support the work

- Begin to develop the open source model, cooperation and collaboration modes, project organization

- Goals for next two workshops, i.e., focus of their agendas

# Plan

- Day 1

- Overviews of architecture trends

- Current status of HPC systems and SW models

- Science Drivers in US, EU, and Japan

- Panel on SW Barriers for HPC, today and tomorrow

- Three evolutionary SW items

- Three revolutionary SW items

- What are the community interaction models to address both evolutionary and revolutionary themes?

# Plan Day 2

- Breakout 1: Technical Roadmap Discussion: What is feasible? What are the top challenges?

- Breakout 2: Collaboration model and funding: How can we work together?

Goals and agenda for next workshop

# Follow on Meetings

- Refine the ideas that emerged from the earlier meetings.

- Incorporate new ideas into the plan.

- Expose the IESP to a wider group of people.

- We would like to get buy in from as many people as possible. Some may not be able to attend the earlier meetings.

# e-Infrastructure in FP7: HPC related aspects

Mme Catherine Riviére (on behalf of DG INFSO/F03)

IESP Workshop Santa Fe, 7-8 April 2009

### **Main contents:**

- e-Infrastructure: the mission

- Framework Programme 7

- Main flagship projects

- GÉANT

- EGEE

- DEISA & PRACE

- ... and scientific data repositories

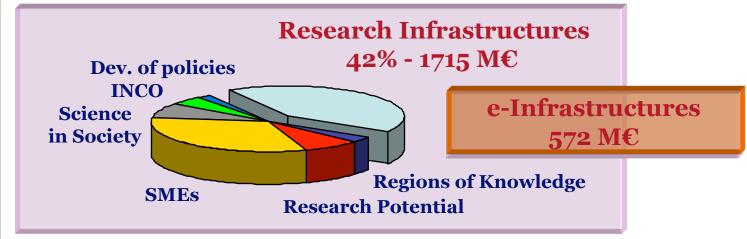

- FP7 'Capacities': RI Call 7 topics

### e-Infrastructure: the mission!

e-Infrastructure refers to the creation of a new research environment in which all European researchers have shared access to unique or distributed scientific facilities (including data, instruments, computing and communications), regardless of their type and location in the world.

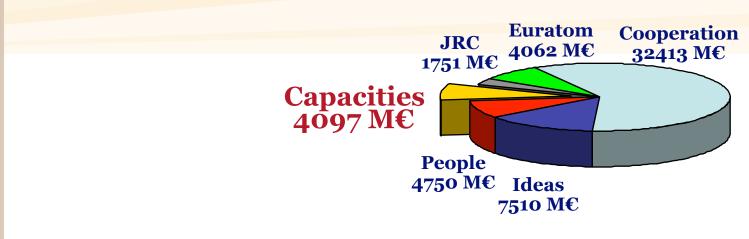

# Framework Programme 7: 2007 to 2013

European Commission Information Society and Media

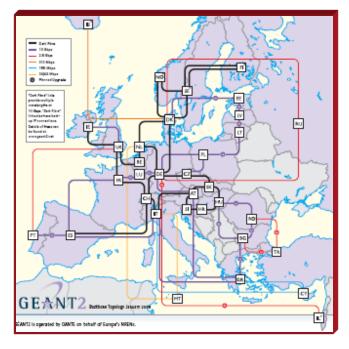

# **GÉANT:** connecting Europe

- Pan-European coverage (40+ countries /3900 universities / 30+ million students)

- Hybrid architecture:

- connectivity at 10 Gb/s (aggregated traffic)

- dark fiber wavelengths (demanding communities)

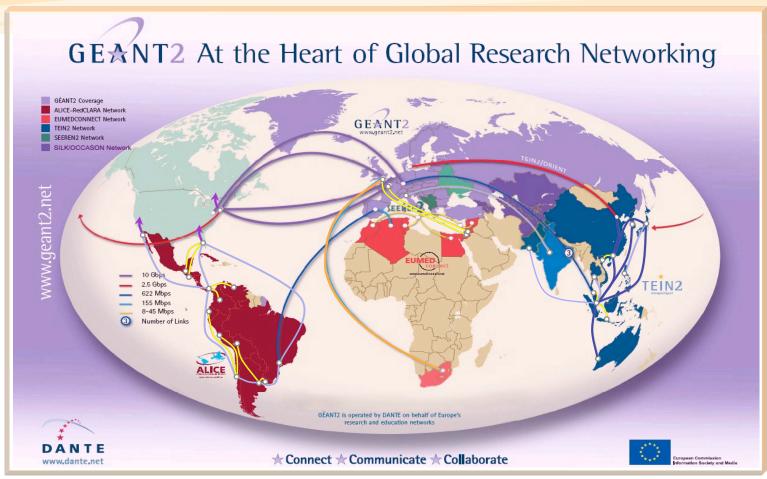

# **Global dimension of GÉANT**

**•••** 6

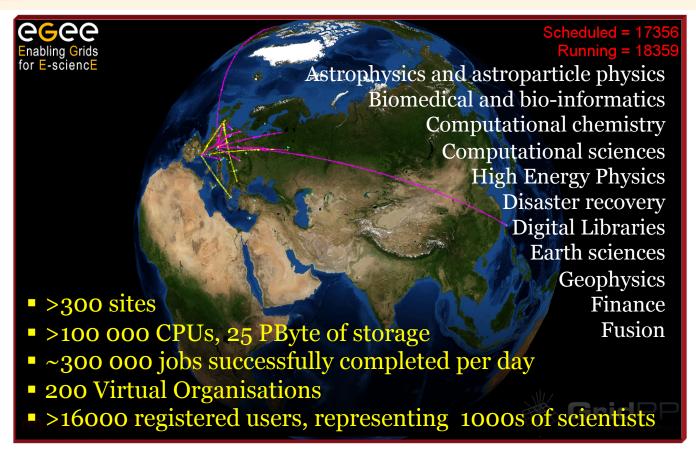

# **EGEE: Tackling Global Challenges**

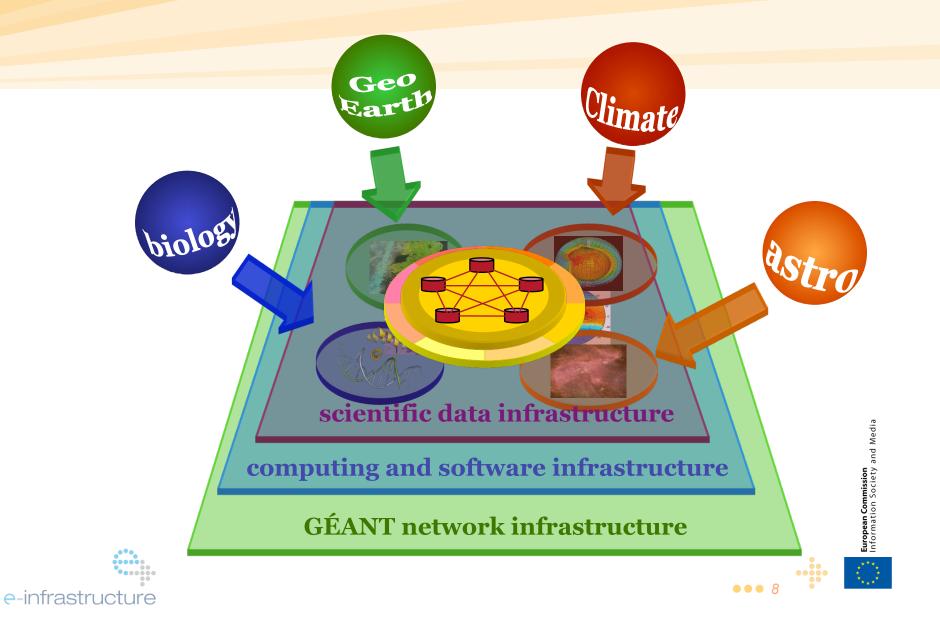

### Scientific Data Infrastructure

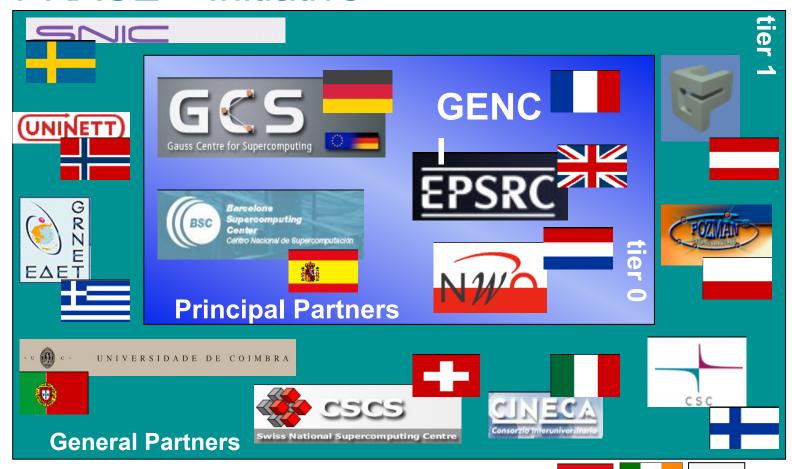

### **DEISA: 'virtual' HPC services**

- 12 sites in 7 countries connected at 10 Gb/s

- Over 22,000 CPUs with an aggregated peak performance of close to 1 Peta flops

- Running larger parallel applications in individual sites

- Enabling workflow applications with grid technologies (UNICORE)

- Providing a global data management service

- Extreme Computing Initiative

# **PRACE:** the preparatory phase

### 18 European countries signed the PRACE MoU!!

• • • 10

# <u>Draft</u> WP2010 topics: RI Call 7: Open 30.07.09; close 24.11.09

- INFRA-2010-1.2.1: Distributed computing infrastructure (DCI)

- INFRA-2010-1.2.2: Simulation software and services

- INFRA-2010-1.2.3: Virtual Research Communities

- INFRA-2010-2.3.1: First <u>implementation phase</u> of the <u>European HPC service</u>

- INFRA-2010-3.3: Coordination actions, conferences and studies supporting policy development, incl. international cooperation

**TOTAL Indicative budget: 115 Million Euro**

# further information

www.cordis.europa.eu/fp7/ict/e-infrastructure/

Konstantinos.Glinos@ec.europa.eu

# **Contents**

- > simulations for predictions (example)

- > science and technology policy in Japan

- > project of the next generation supercomputer

- > grand challenges in applications

- > collaborations with private sectors

- > concluding remarks

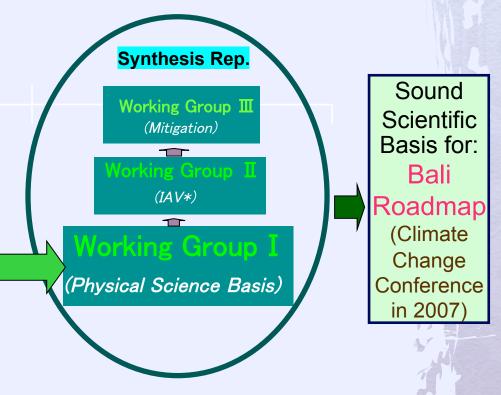

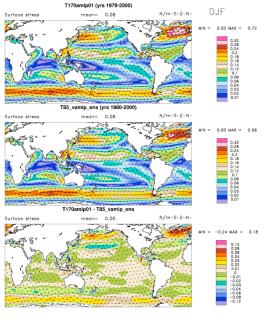

# Contribution to the IPCC by the Earth Simulator

### Global warming projections

by climate modeling groups <under the MEXT\* research project>

# Earth Simulator

### Some of major outcomes

- Highest resolution coupled model

- → "Very likely" Attribution (stronger confirmation)

- ◆Super-high resolution Global Atmospheric model → Projection of increased strength of Typhoons & Hurricanes (new finding)

- ◆ Earth system model

- → Carbon cycle feedback causing additional warming (new finding)

Fourth Assessment Report (2007)

(\* IAV = Impact, Adaptation and Vulnerability)

# 6

### Outline of the 3rd S&T Basic Plan

### 1. Fundamental Concept

- Recent situation revolving around S&T

- Basic stance toward the 3rd plan

- Fundamental ideas and policy goals

- Total gov'tal R&D investment: \25 trillion (\$200 billion)

### 3. S&T system reforms

- Fostering S&T personnel and providing opportunities

- Progress in science and leading to innovation

- Upgrading infrastructures for S&T promotion

- Strategic commitment on international S&T activities

### 2. Strategic Priority Setting in S&T

- Promotion of basic researches

- Prioritization of R&D for policy-oriented subjects

<u>Primary prioritized areas</u>; Life science, IT,

Environmental sciences, Nano-tech. & materials

<u>Secondary prioritized areas</u>; Energy,

MONODZUKURI tech., Infrastructure, Frontier (outer space & oceans)

- Promotion strategy for the prioritized areas

### 4. Public Confidence and Engagement

- Responsible actions regarding ethical, legal and social issues

- Reinforcement of accountability and public relations of S&T activities

- Promotion of public understanding of S&T

- Facilitation of public engagement with S&Trelated issues

### 5. Missions of the CSTP

- More efficient and effective management of governmental R&D

- Break of institutional or operational bottle necks

- Follow-up of the Plan and promotion of progress in S&T

#### Key Technologies of National Importance

Ocean & earth exploration system

Fast breeder reactor technology

: projects RIKEN is conducting

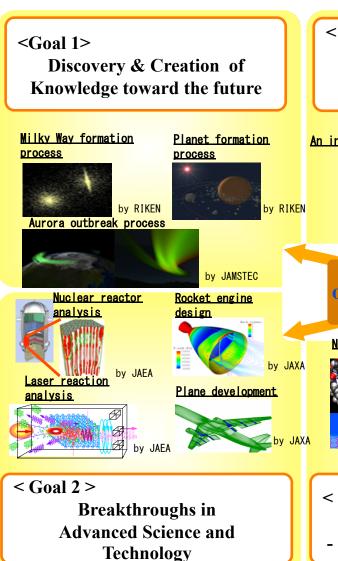

# Six Goals of the Third Science and Technology Basic Plan (FY2006-FY2010)

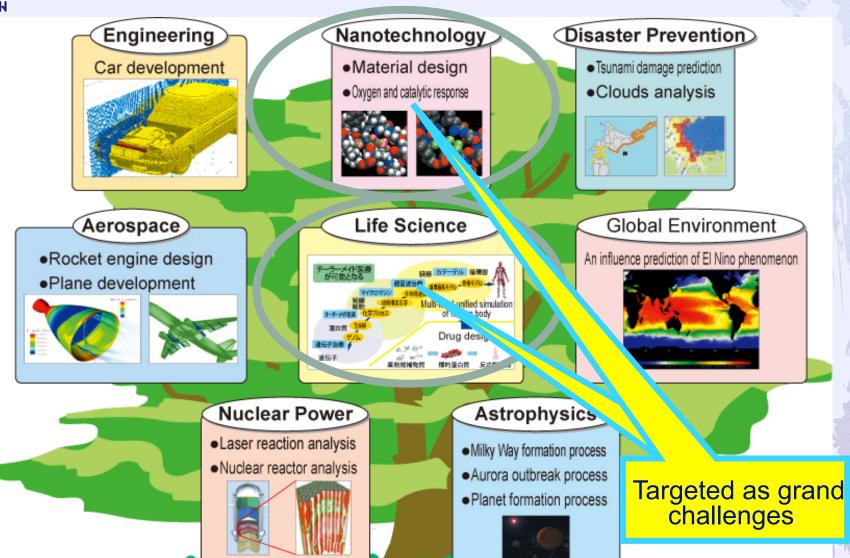

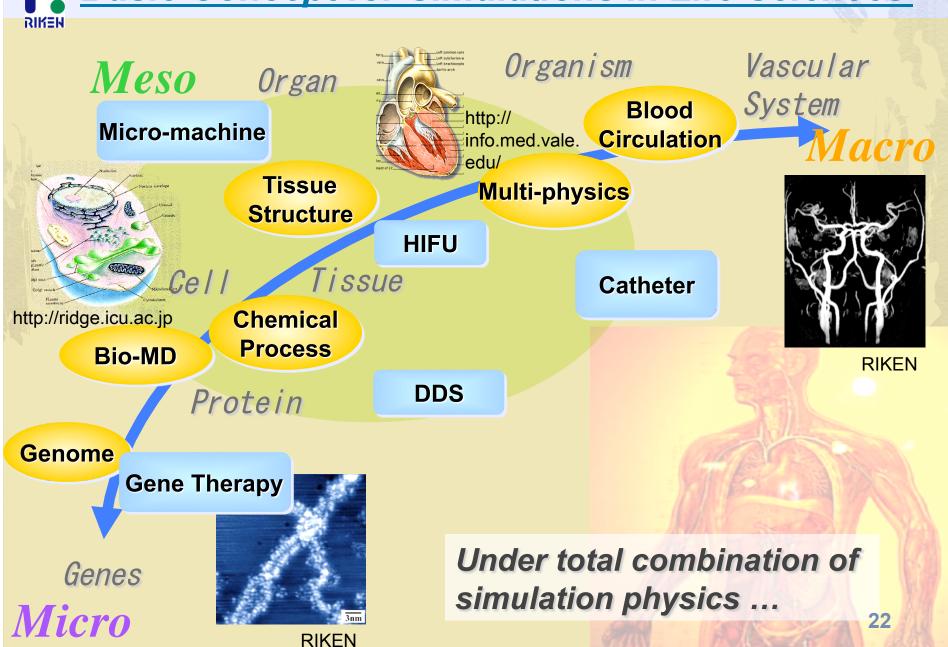

< Goal 3 > **Sustainable Development** - Consistent with Economy and **Environment** -An influence prediction of El Nino phenomenon by JAMSTEC **Development and Application** of Advanced High-performance Supercomputer Nano technology Car development by NISSAN by IMS < Goal 4 > **Innovator Japan** - Strength in Economy & Industry -

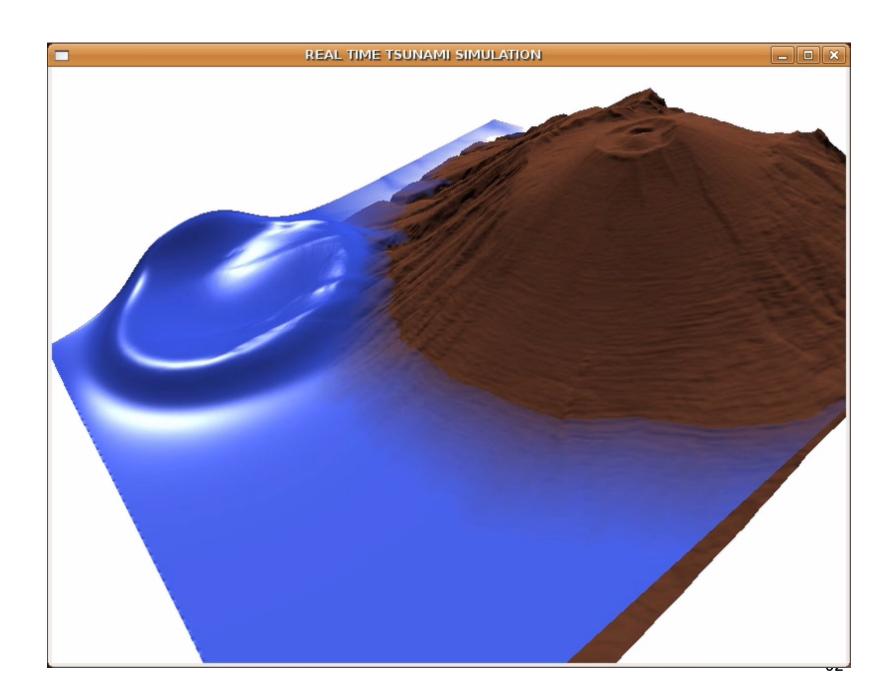

< Goal 5 > **Good Health over Lifetime** Multi-level unified simulation Realization of tailor maid medical care Drug design Gene therapy by Univ. of Tokyo and RIKEN Clouds analysis Tsunami damage prediction by Tohoku by MRI Univ. < Goal 6 > Safe and secure Nation

# CACST: Center for Advanced Computational Science and Technology (tentative name)

Computer science and Computational science

Both researchers will gather and expect to develop new research fields and methodologies

• Currently, we are designing the center and operation policy of

the supercomputer

The users will be chosen by a new committee independent from RIKEN to pick up valuable subjects

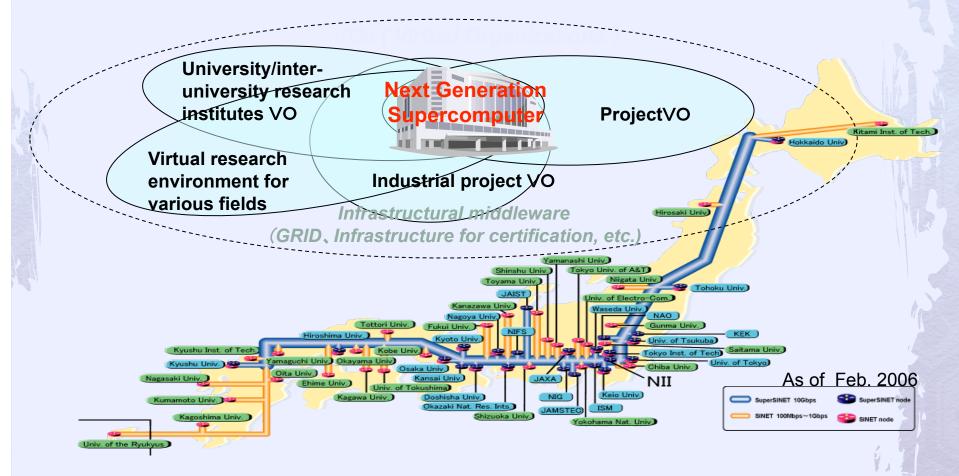

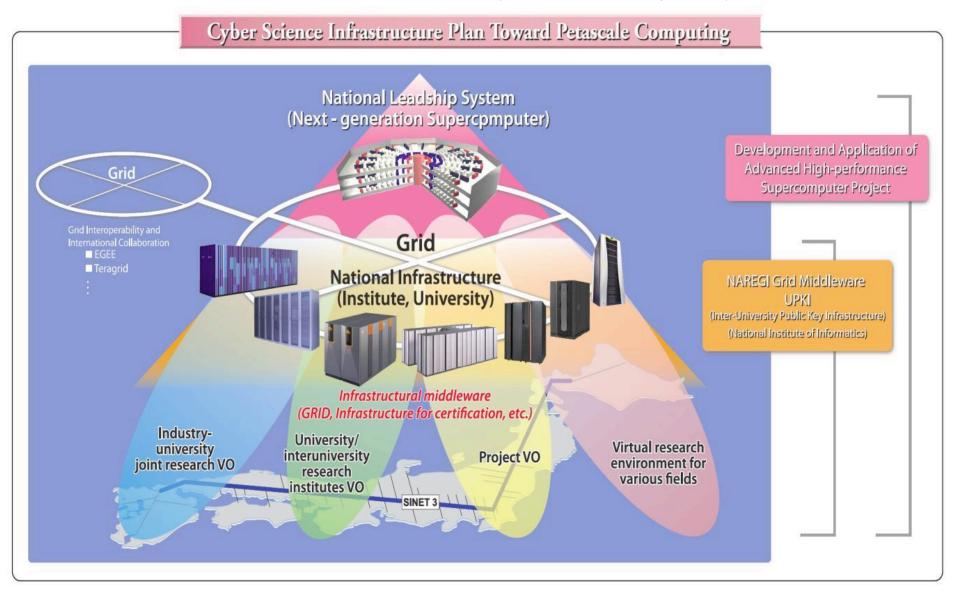

# The Location of the Next Generation Supercomputer Center

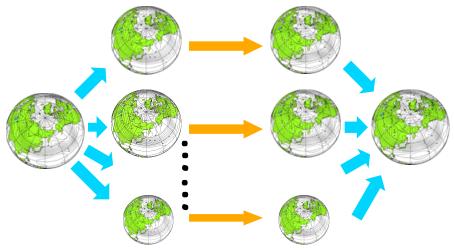

#### Relations with Other Supercomputer Centers

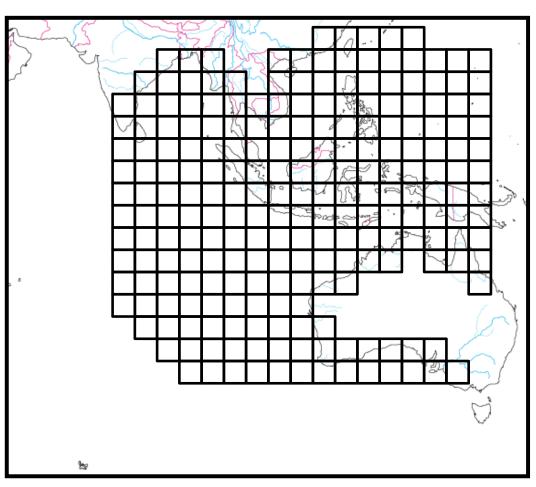

Cyber Science Infrastructure Plan

Proposed by National Institute of Informatics (NII)

(Note)V O: Virtual Organization

FY2006: 3,547Million yen / FY2007: 7,736Million yen

FY2006~FY2012 (total budget expected) about 110billion yen

#### 1. Purpose of policy

Development and implementation of the world's most advanced and high-performance Next-Generation Supercomputer, and to develop and disseminate its usage technologies, as one of Japan's "Key Technologies of National Importance" (National Infrastructure).

#### 2. Expected effects

As an important tool for simulation, supercomputing needs to be developed further. This project aims to bring the Next-Generation Supercomputer to completion in 2012. In order to maintain world-leading position in variety of areas, the following academic-industrial collaboration activities will be conducted under the initiative of MEXT.

- (1) Development and implementation of the world's most advanced high-performance Next-Generation supercomputer

- (2) Development and dissemination of software that makes optimum use of the supercomputer

- (3) Establishment of the world's most advanced and highest standard supercomputing Center of Excellence, which includes the Next-Generation Supercomputer

#### 3. Project Framework

- Integrated development of computer and software

- Establishment of nationwide academic-industrial collaborative structure, with RIKEN as the project headquarters

- A new law has been introduced for the framework of usage and administration

#### Goals of the Next Generation Supercomputer Project

- Development and installation of the most advanced high performance supercomputer system

- 2. Development and wide use of application software to utilize the supercomputer to the maximum extent

- Provision of flexible computing environment by sharing the next generation supercomputer through connection with other supercomputers located at universities and research institutes

- 4. Establishment of "Advanced Computational Science and Technology Center (tentative name)"

**Advisory**

**Board**

## **Project Organizations**

#### **MEXT: Policy & Funding**

Office for Supercomputer Development Planning

**Project Committee**

#### **Industry Users**

Industrial Committee for Promotion of Supercomputing

#### **R&D Scheme**

#### **RIKEN: Project HQ**

Next-Generation

Supercomputer R&D Center

(Ryoji Noyori)

Project Leader: Tadashi Watanabe

NII: Grid Middleware and Infrastructure

IMS: Nano Science Simulation

Riken Wako Institute: Life Science Simulation

#### **Evaluation Scheme**

**Evaluation Committee**

Universities, Laboratories, Industries

(Note) NII: National Institute of Informatics, IMS: Institute for Molecular Science

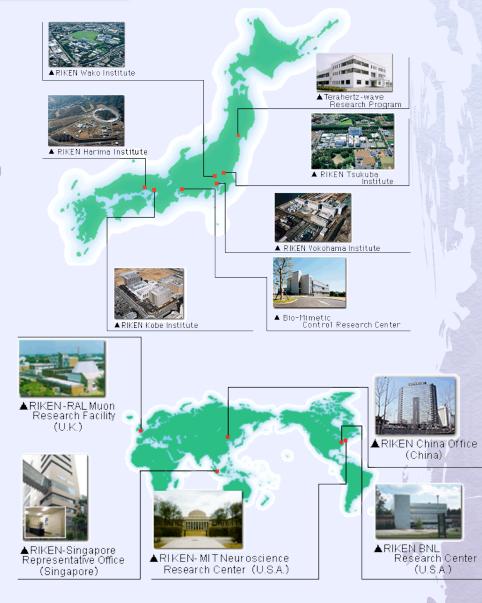

## RIKEN and Advanced Center for Computing and Communication

#### RIKEN

- comprehensive research in science and technology (excluding only humanities and social sciences)

- physics, chemistry, medical science, biology, and engineering extending from basic research to practical application

- 7 campus in Japan, 5 outside Japan

- about 3000 researchers

- an Independent Administrative Institution under the Ministry of Education, Culture, Sports, Science & Technology (MEXT) from 2003

- Advance Center for Computing & Communication

- Providing RIKEN researchers with computer resources and network services

- Operating RSCC(RIKEN Super Combined Cluster)

# Policy and Outline of A Next Generation Supercomputer Project

#### Purpose of policy:

development, installation and application of an advanced high performance supercomputer system, as one of Japan's "Key Technologies of National Importance"

#### **Total Budget:**

about 115 billion Yen (0.7 billion Euros)

100% national funds

#### **Period of Project:**

FY2006 - FY2012

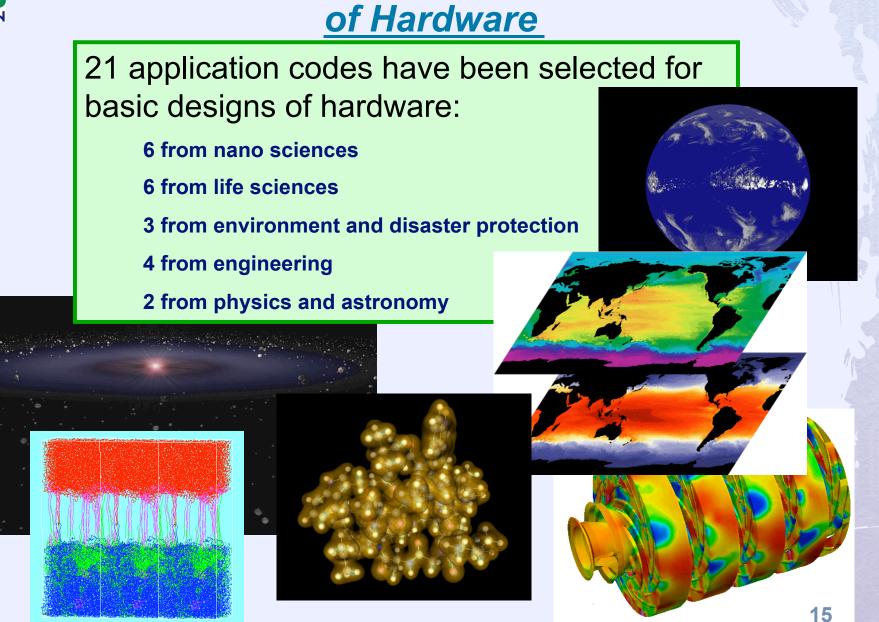

# Applications Selected for Basic Designs of Hardware

## The Next-Generation Supercomputer project

The Next-Generation Supercomputer project started in 2006 which is being carried out by RIKEN, with partners in industry, universities, and the government, under an initiative by MEXT (the Ministry of Education, Culture, Sports, Science and Technology).

Due to be ready in 2012, the peta-scale computing by the new supercomputer will ensure that Japan continues to lead the world in science and technology, academic research, industry, and medicine.

simulation

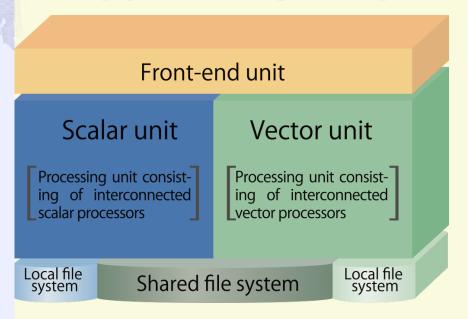

#### [System configuration]

The Next-Generation Supercomputer will be hybrid general-purpose supercomputer that provides the optimum computing environment for a wide range of simulations will be performed in processing units that are suitable for the particular

•Parallel processing in a hybrid configuration of scalar and vector units will make larger and more complex simulations possible.

## Schedule of Project

|           |                                                            | 2006                                    | 2007                                          | 2008            | 2009                            | 2010                | 2011                         | 2012        |

|-----------|------------------------------------------------------------|-----------------------------------------|-----------------------------------------------|-----------------|---------------------------------|---------------------|------------------------------|-------------|

|           |                                                            |                                         |                                               |                 |                                 | Operation 4         | Completion                   | Pa -        |

| System    | Processing unit                                            | Conceptual Detai                        |                                               | led design      | Prototype and Production and ad |                     | n, installation,<br>justment |             |

|           | Front-end unit<br>(total system<br>software)               |                                         | Basic<br>design                               | Detailed design | Production a                    | and evaluation      | Tuning and                   | improvement |

|           | Shared file<br>system                                      |                                         | Basic<br>design                               | Detailed design | Production                      | n, installation, an | d adjustment                 |             |

| Ŋ         | Next-Generation<br>Integrated<br>Nanoscience<br>Simulation | Development, production, and evaluation |                                               |                 |                                 |                     | Verification                 | . 5         |

|           | Next-Generation<br>Integrated<br>Life Simulation           | Development, production, and evaluation |                                               |                 |                                 | n                   | Verification                 |             |

| Buildings | Computer building                                          |                                         | Design                                        | Constr          | uction                          |                     |                              | *           |

|           | Research<br>building                                       |                                         | Desig                                         | gn Co           | nstruction                      |                     |                              | V.          |

| Operation |                                                            |                                         | Decisions on policies and systems Preparation |                 |                                 |                     | Operation                    |             |

#### Major Applications of Next Generation Supercomputer

# Task Forces to Develop the Grand Challenges Application Codes

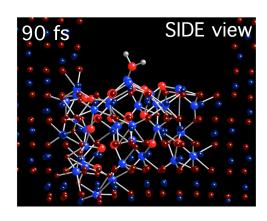

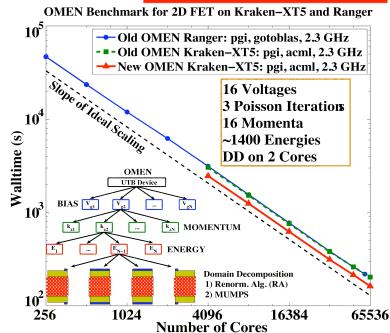

#### Nano Science

Conducting Institute: Institute for Molecular Science (IMS)

Budget for 2008 Fiscal Year: 5.6 Million US Dollars

Contributing Institutes and Universities: 6

#### Life Science

Conducting Institute: RIKEN

Budget for 2008 Fiscal Year: 14.4 Million US Dollars

Contributing Institutes and Universities: 14

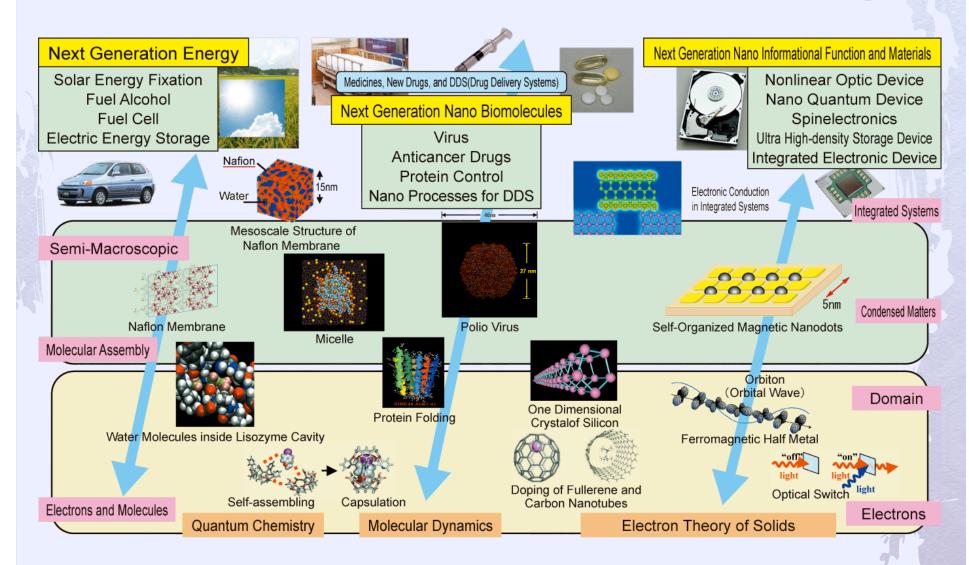

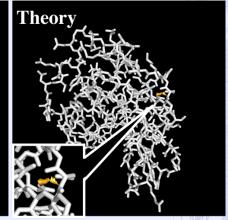

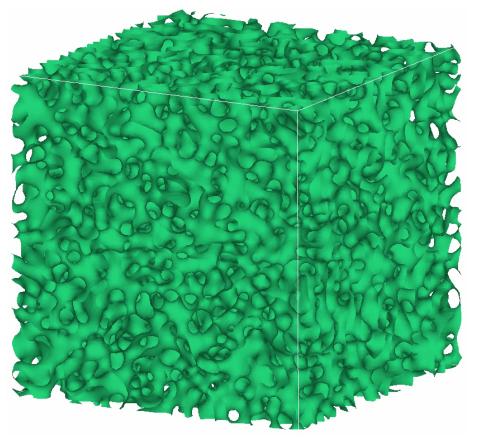

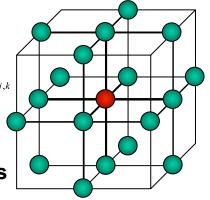

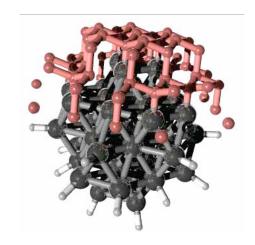

#### Basic Concept for Simulations in Nano-Science

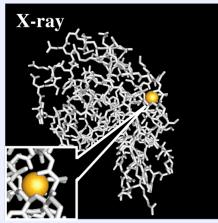

# Molecular Recognition of Proteins Reproduced by 3D-RISM

Water molecules and lons recognized by a protein

#### Cellulase

A water molecule recognized by enzyme-cellulose complex.

Courtesy of IMS

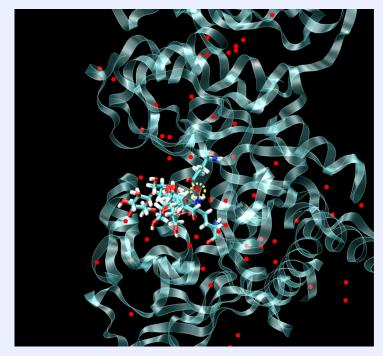

#### Basic Concept for Simulations in Life Sciences

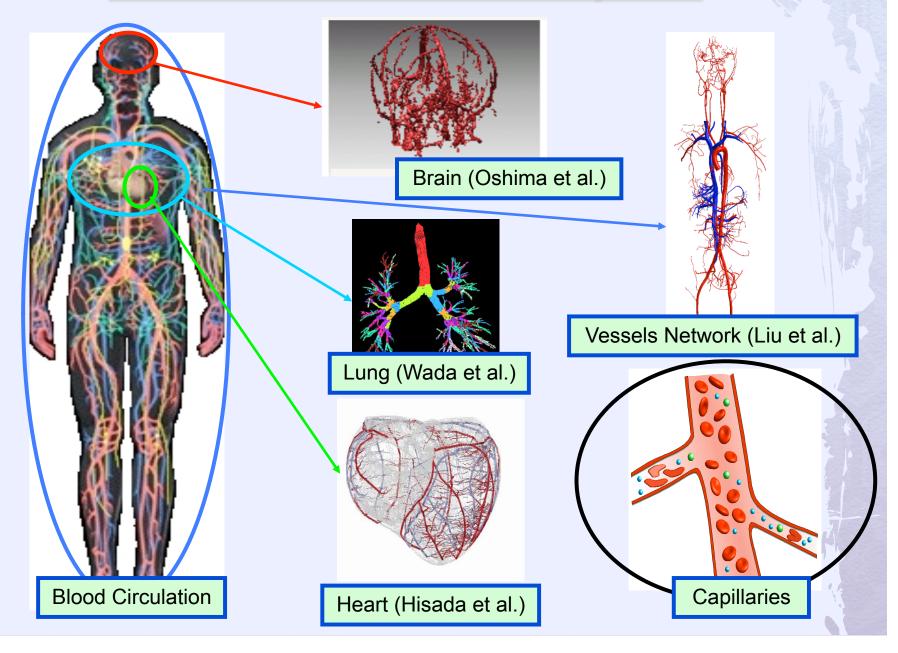

## Simulation for Circulation System

# Promotion Program of Supercomputers for Industries

#### **Industrial Committee for Super Computing Promotion**

- > established in 2006

- participated by more than 170 companies from various industries

- activities: simulation of engines, analyses of car body, material and polymer simulation, weather simulation

#### Recent Activities of ICSCP

seminar and expo to industrial researchers about usefulness of simulations

# Promotive Activities by Public Computer Centers for Industrial Use of HPC

MEXT is conducting a project to stimulate use of public high-tech facilities for industrial R&D

Earth Simulator and computer centers of major universities provide their computer resources for industries

test use for free and productive use for charged

Computer Center of Tokyo University

Fields of about 40 applicants from industries

drug design semi conductors aerodynamics functional materials banking system fuel cell noise control of cars and bullet train catalyst internet search engine audio interpretation

## **Concluding Remarks**

- > The next generation supercomputer project aims at:

- ■to keep cutting-edge computer technologies inside Japan

- ■to prompt application software developing activities

- ■to rear young scientists for HPC fields

- Consequently, we expect:

- ■to maintain competitiveness in worldwide HPC technology

- ■to innovate R&D in industries by computational science

- ■to create new IT businesses such as SaaS (service as a software)

- > Then, we accomplish:

- ■to reinforce science infrastructure in Japan

- ■to retain high economic activities

# International Exascale Software Program

Abani K. Patra

Office of Cyberinfrastructure,

National Science Foundation

## **Drivers**

- Advances in most branches of science and engineering are critically dependent on increasingly complex multi-scale, multi-physics, data driven computations and analysis.

- Complexity of Systems

- Moore's Law and Beyond -- Multicore, manycore, ...

- Heterogeneous machines

- Data Intensive Scalable Computing

- Workflows, Grids, Clouds ...

- All this complexity dealt with by software and tools!

- Support for which is ad hoc, disjoint and spread across divisions, directorates and agencies!

First Cosmological simulations to include black hole physics by Di Matteo et. al. at Carnegie Mellon funded by OCI and MPS/AST.

Optimal siting of oil exploration platform estimated by using simulation and optimization tools to maximize product

Abani K. Patra apatra@nsf.gov

Office of Cyberinfrastructure

## How?

- NSF/OCI engaged in actualizing "CI Vision..." -- Atkins et. al.

- Computational Science -- the unifying theme across many threads that lead to successful use of computational hardware in the discovery and innovation process -- support for which is ad hoc, disjoint and spread across divisions and directorates

- Advisory Committee on Cyberinfrastructure (ACCI) has formed sub-committees -- "Task Forces" to deal with multiple aspects

-- HPC, Grand Challenges, Software, Campus Bridging, Data, LWD

# "CI Task Force"

- "opportune time to carefully investigate alternate mechanisms and methodologies for ensuring that the research, development and sustenance of the nation's software and tool infrastructure is well positioned to help our scientists with a competitive advantage and not a disadvantage."

- The charge to the group comprises of the following:

- Characterize and estimate the magnitude and scope of need

- Develop initiatives and programs to promote future growth, development and sustainability

of the software and tool infrastructure needed for transformative research and innovation

leading to industrial competitiveness and knowledge leadership.

- Analyze institutional and other barriers at NSF to promoting and supporting such an infrastructure.

# Questions?

- What are the new applications that are emerging or likely to emerge in the coming decade?

- How can NSF best stimulate development of exascale software applications?

- How can useful software that has been developed as part of the exascale effort be sustained beyond the development period?

- What systems software will be required? Distributed systems support, programming environments, runtime support, datamanagement user tools?

# Questions?

- What application support environments will be needed?

Application packages, numeric and non-numeric library packages, problem-solving environments?

- How can NSF aid or catalyze developments that make it possible to use the same tools, including compilers, debuggers and performance tools, on system scales all the way down to the typical researcher's laptop or desktop?

- What education and training actions should be considered to prepare researchers, students and educators for future cyberinfrastructure?

Improving HPC Software

## IESP Workshop #1

Santa Fe, New Mexico: April 7 & 8

- □ Version 1.0 started by Ken Kennedy in 2006...

- Effort was re-launched in 2008

- Initial planning meeting at SC08

- This meeting sponsored by DOE & NSF in coordination with EU and Japanese

- 68 attendees

- Subsequent meetings will be held and sponsored by Europe (end of June) and Japan (October)

- Workshop reports will focus plans and identify issues

- □ PIES?

## Agenda

- Today

- Goals and HPC Software Status

- Science drivers and HPC plans: Japan

- Architectural trends for HPC

- Science drivers and HPC plans: Europe

- Software Barriers for HPC, today and tomorrow

- Science drivers and HPC plans: Europe: USA

- Tomorrow

- Breakout groups:

- Tech Roadmap, Collaboration / Coordination models

### **IESP** Goal

Improve the world's simulation and modeling capability by improving the coordination and development of the HPC software environment

Workshops:

Build an international plan for developing the next generation open source software for scientific high-performance computing

Then Do It...

## Components / Workshop Charge

- Outline of what a plan would include, and possible outcomes

- Assess the software needs for peta/exascale computation

- Explore how to develop a community architecture roadmap

- Gather and analyze existing R&D plans for addressing extreme scale; what is missing?

- Identify key technical areas to be included in plan

- Begin development of a roadmap for peta/exascale software

- Identify R&D models that enable laboratories, universities, and vendors to co-develop coordinated open source HPC software

- Examine funding and governance models that support international development

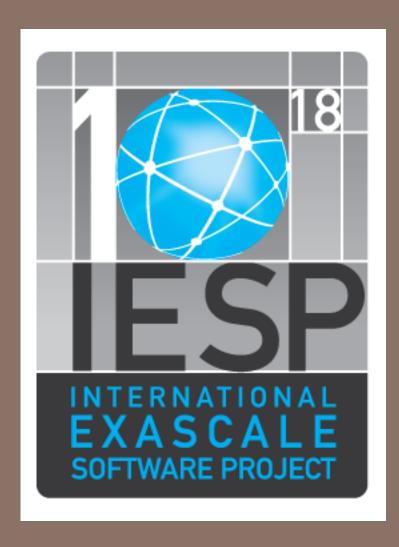

## A Running Start: www.exascale.org

#### White papers

- Musings on the Path Toward Exascale, Robert Lucas ISI/USC

- BSC Vision Towards Exascale, Mateo Valero, BSC

- Software Challenges of Extreme Scale Computing, Michael Heroux Sandia National Laboratory

- Software and Exascale Computing, Bill Camp Intel Corporation

- Application Analysis and Porting in the PRACE Project, Peter Michielse Netherlands National Computing Facilities Foundation (NCF)

- The Application Perspective Seeking Productivity and Performance, David Barkai Intel Corporation

- EDF white paper, J.Y. Berthou and J.F. Hamelin EDF R&D

- The Biggest Need: A New Model of Computation, Thomas Sterling Louisiana State University

- NSF IESP Whitepaper, Abani Patra, Rob Pennington, Ed Seidel Office of Cyberinfrastructure, National Science Foundation

- A Proposal for a Capability Centers Consortium, Bill Gropp, Mark Snir NCSA and the University of Illinois at Urbana-Champaign

- Slouching Towards Exascale, Rusty Lusk, Argonne National Laboratory

- A Collaboration and Commercialization Model for Eascale Software Research, Mark Seager and Brent Gorda, Lawrence Livermore National Laboratory

- The Case for A Hierarchal System Model for Linux Clusters, Mark Seager and Brent Gorda, Lawrence Livermore National Laboratory

- IESP Whitepaper: PDE-based applications and solvers at extreme scale, DavidKeyes,

Columbia University & SciDAC TOPS project

#### Outline: HPC Software

- □ Current State: HPC Software

- □ Background: Activities in Europe and Japan

- The Changing Architecture

- □ The IESP Workshops

- Roadmap and Outcomes

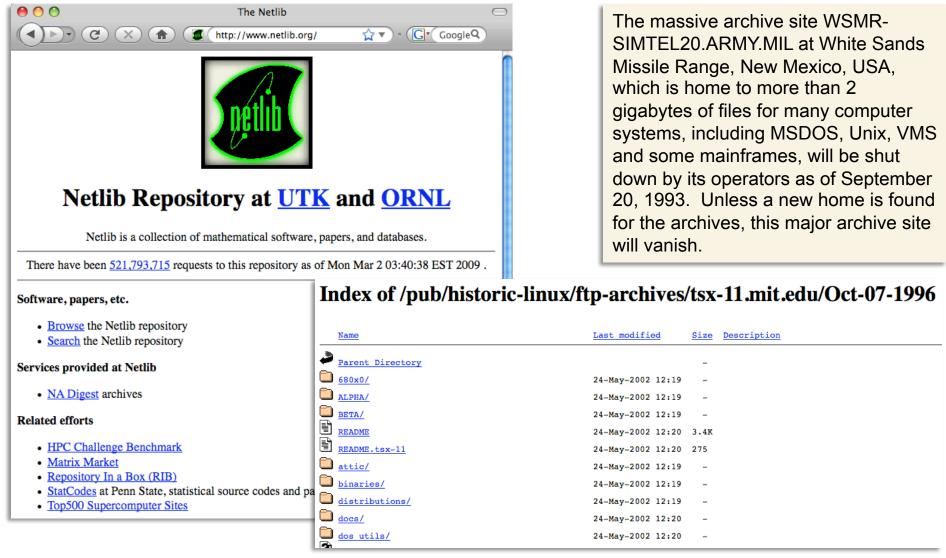

# The Open Source Community Provides Most of the World's HPC Software

## The Community is Diverse and Robust

#### In the last 10 years, galvanization of Open Source development dramatically improved software

#### A very small sample:

- Linux Operating System, libc

- Python, Perl

- PAPI, TAU, Kojak

- dCache

- UPC

- MPICH, OpenMPI

- ScalAPACK

- JuBE

- □ Vislt

- GASNet, ARMCI/GA

- CFEngine, bconfig

- Ganglia

- SLURM, Cobalt

- Dyninst

- Torque/Moab, OpenPBS

- Charm++

- pNetCDF, HDF5

- GridFTP

- FFTW

- PVFS

#### A Long History of Collaboration & Sharing

The Result....

# Open Source HPC Software Stacks for Small Linux Clusters are Everywhere

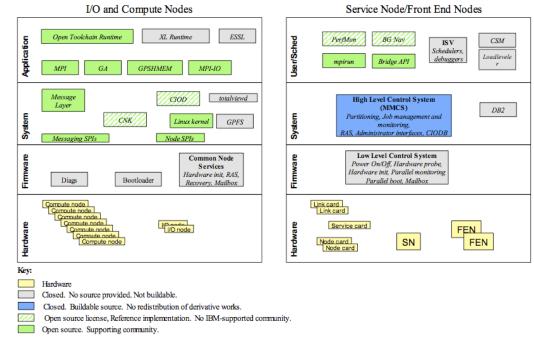

# Just Buy It? Scalability Thins the Market

- For some markets, a closed source business model continues to work well

- Single-node optimized math libraries & compilers

- Debuggers for small clusters

- Some queuing systems, parallel file systems, HSMs

- Small cluster applications: Fluent,CFD++, etc

#### **BG/P Software Stack Source Availability**

# Why Seek to Improve This?

- The largest scale systems are becoming more complex, with designs supported by large consortium

- The software community has responded slowly

- Significant architectural changes arriving

- Software must dramatically change

- Our ad hoc community coordinates poorly, both with other software components and with the vendors

- Computational science could achieve more with improved development and coordination

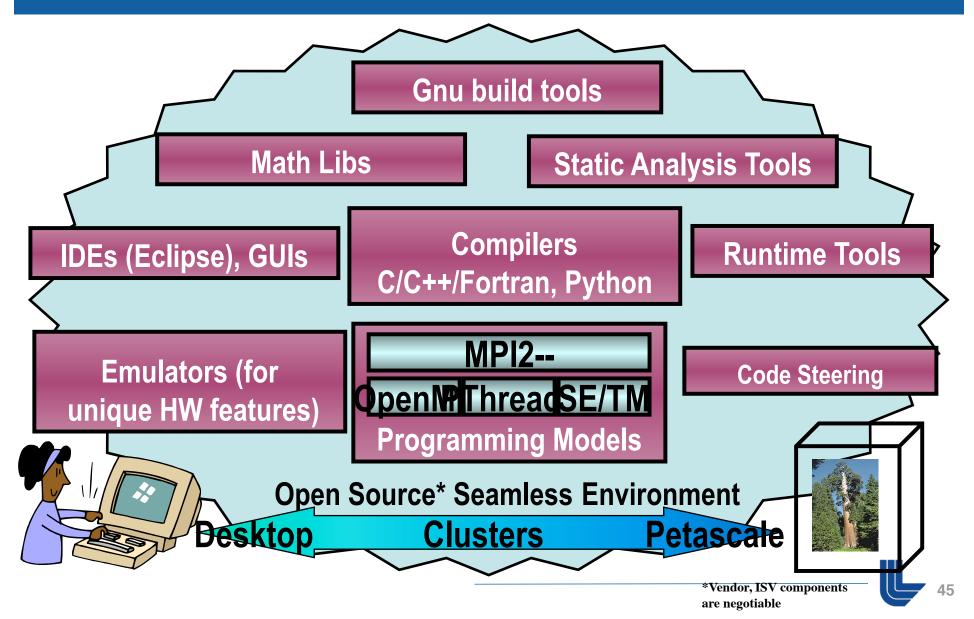

## Extreme-Scale Platform Design:

Industrial revolution and globalization has arrived

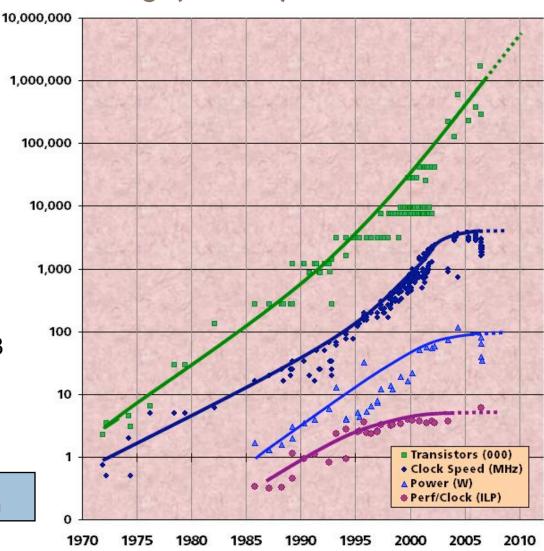

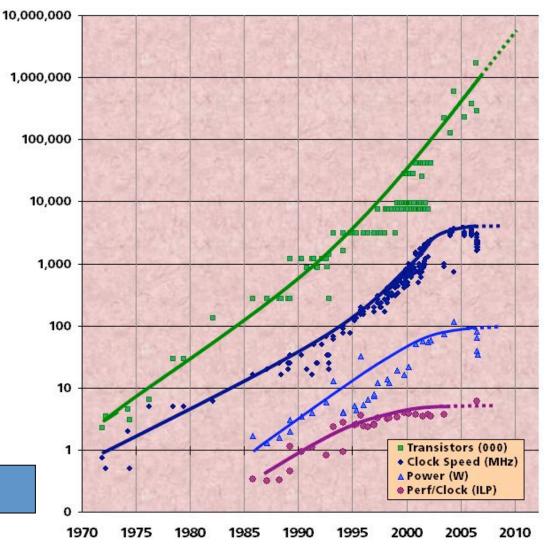

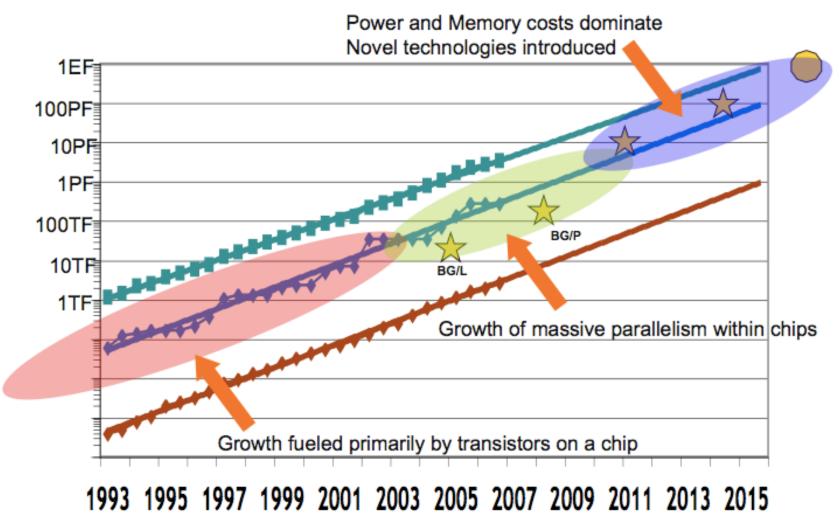

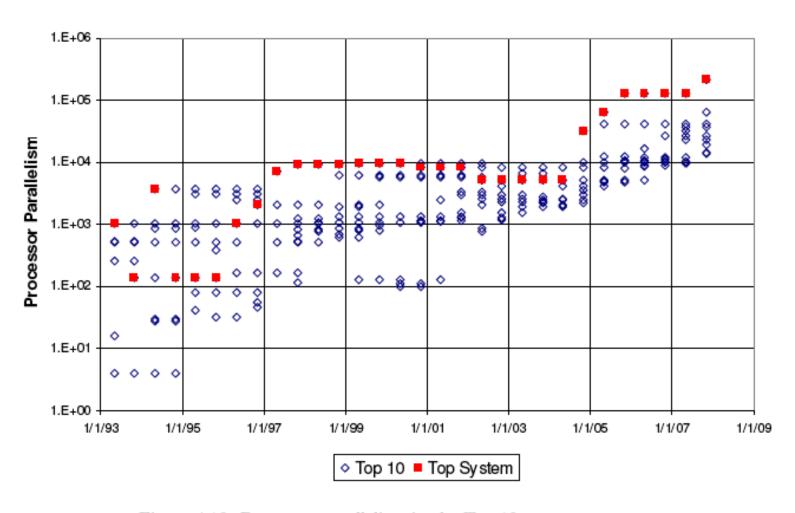

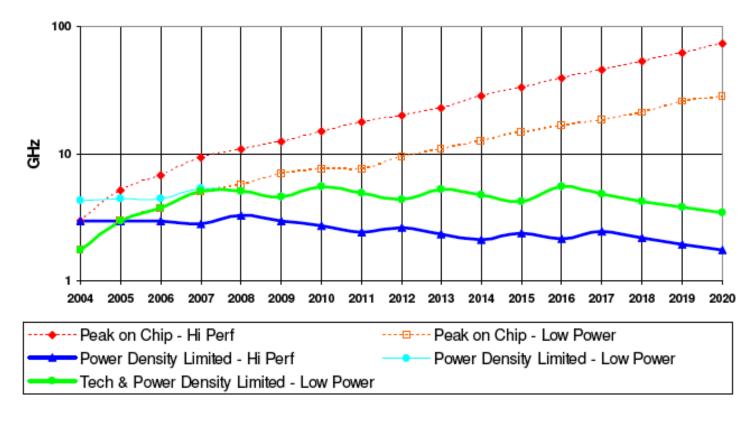

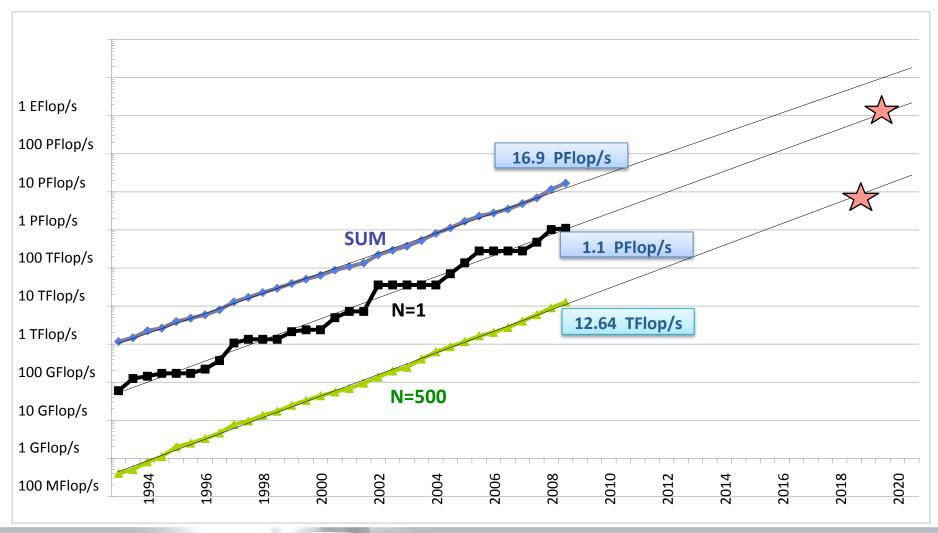

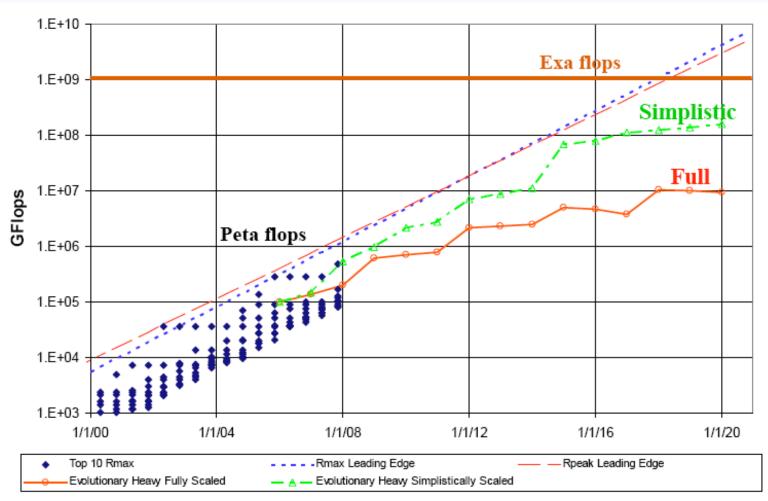

# Traditional Sources of Performance Improvement are Flat-Lining (2004)

- New Constraints

- 15 years of exponential clock rate growth has ended

- Moore's Law reinterpreted:

- How do we use all of those transistors to keep performance increasing at historical rates?

- Industry Response:

parallelism doubles every 18

months *instead* of clock

frequency!

Figure courtesy of Kunle Olukotun, Lance Hammond, Herb Sutter, and Burton Smith

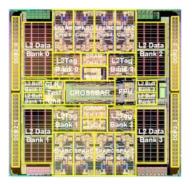

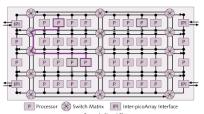

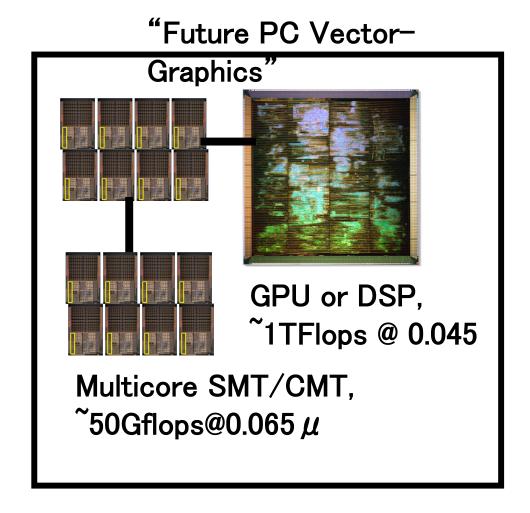

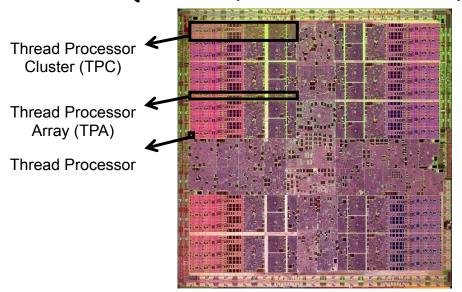

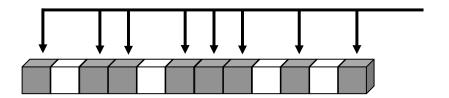

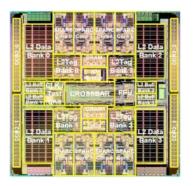

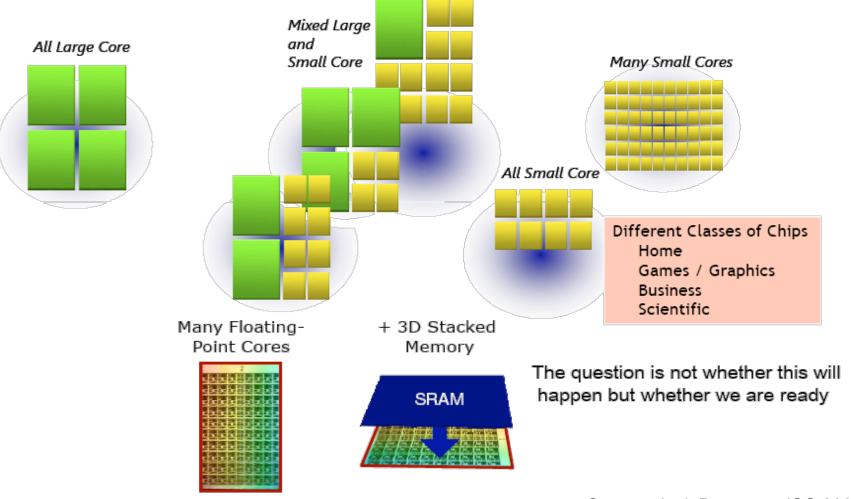

# Multicore comes in a wide variety

- Multiple parallel general-purpose processors (GPPs)

- Multiple application-specific processors (ASPs)

Intel Network Processor

1 GPP Core

16 ASPs (128 threads)

You Are Here

Sun Niagara 8 GPP cores (32 threads)

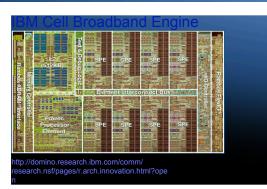

IBM Cell 1 GPP (2 threads) 8 ASPs

Picochip DSP 1 GPP core 248 ASPs

Intel 4004 (1971):

4-bit processor,

2312 transistors,

~100 KIPS,

10 micron PMOS,

11 mm² chip

"The Processor is the new Transistor" [Rowen]

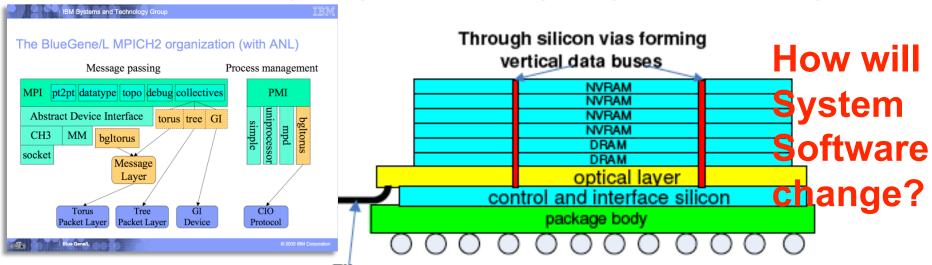

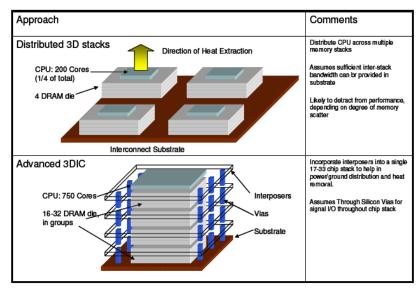

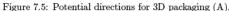

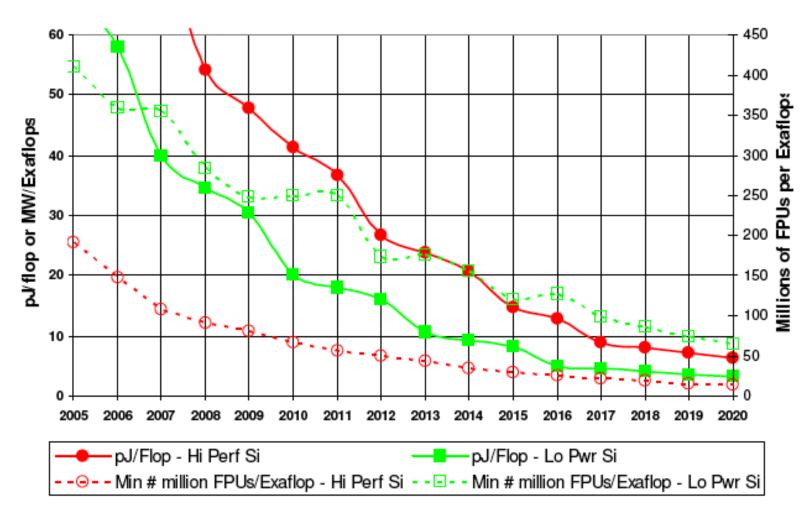

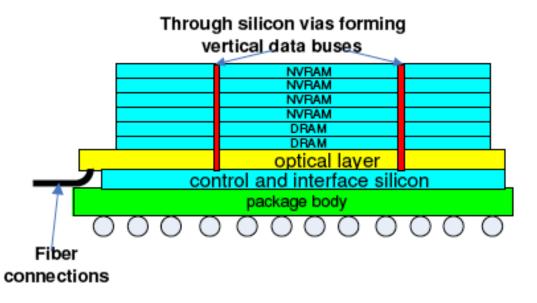

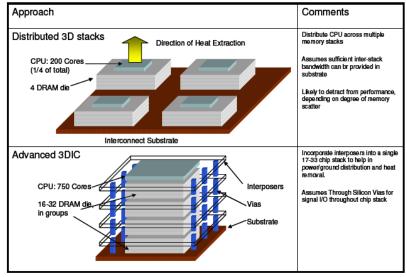

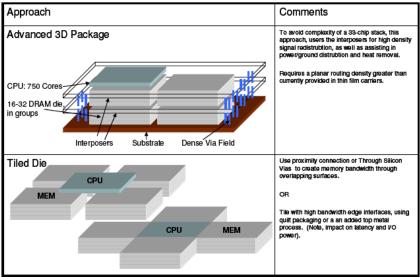

# 3D Packaging: Changing Paradigms

#### Fiber connections

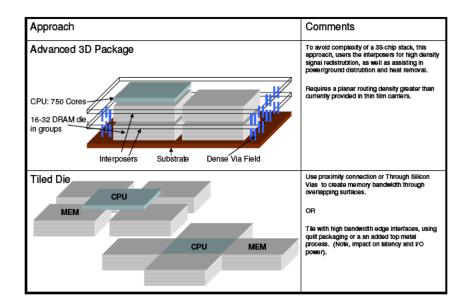

Figure 7.6: Potential directions for 3D packaging (B).

# Vision of Photonic NoC Integration

Courtesy: Keren Bergman, Columbia

# Power and Programming Models

# To Build a SW Roadmap & Plan:

- What do we use today?

- What we need tomorrow?

- How we can fill in the gaps?

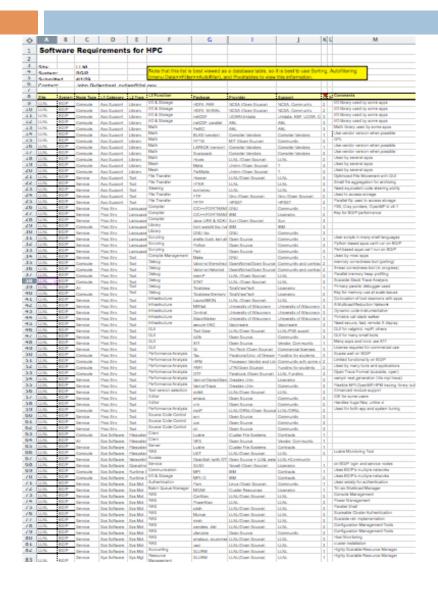

# Inventory Exercise...

- Broadly divide software and functionality into hierarchical categories:

- □ I/O Storage

- Math Libraries

- Performance Tools

- □ Etc.

- □ Where it is run...

- Service node, I/O nodes, compute nodes, login nodes, etc

# Example Snippets: ORNL XT3

| <b>\rightarrow</b> | Α      | В        | С         | D           | Е        | F             | G                  |                  |

|--------------------|--------|----------|-----------|-------------|----------|---------------|--------------------|------------------|

| 1                  | Soft   | ware     | Requir    | ements      | for H    | PC            |                    |                  |

| 2                  |        |          |           |             |          |               |                    |                  |

| 3                  | Site:  |          | ORNL      |             |          |               |                    |                  |

| 4                  | Syster | n:       | Cray XT   | 3           |          | Note that th  | is list is best vi | ewed as a da     |

| 5                  | Submi  | itted    | 8/25/06   |             |          | (menu Data    | >>Filter>>Auto     | ofilter), and Pi |

| 6                  | Conta  | ct:      | Jeff Vett | er, vetter@ | ornl.gov |               |                    |                  |

| 7                  |        |          |           |             |          |               |                    |                  |

| 8                  | Site   | System   | Node Type | L1 Category | L2 Type  | L3 Function   | Package            | Provider         |

| 9                  | ORNL   | Cray XT3 | All       | App Support | Library  | I/O & Storage | HDF5_PAR           | NCSA             |

| 10                 | ORNL   | Cray XT3 | All       | App Support | Library  | I/O & Storage | HDF5_SERIAL        | NCSA             |

| 11                 | ORNL   | Cray XT3 | All       | App Support | Library  | I/O & Storage | netCDF             | UCAR/Unidata     |

| 12                 | ORNL   | Cray XT3 | All       | App Support | Library  | I/O & Storage | netCDF, parallel   | ANL              |

| 13                 | ORNL   | Cray XT3 | Compute   | App Support | Library  | Math          | PetSC              | ANL              |

| 14                 | ORNL   | Cray XT3 | Compute   | App Support | Library  | Math          | Aztec              | Sandia           |

| 15                 | ORNL   | Cray XT3 | Compute   | App Support | Library  | Math          | BLAS               | AMD              |

| 16                 | ORNL   | Cray XT3 | Compute   | App Support | Library  | Math          | FFTPack            | Netlib           |

| 17                 | ORNL   | Cray XT3 | Compute   | App Support | Library  | Math          | FFTW               | MIT              |

| 18                 | ORNL   | Cray XT3 | Compute   | App Support | Library  | Math          | LAPACK             | AMD              |

| 19                 | ORNL   | Cray XT3 | Compute   | App Support | Library  | Math          | MUMPS              | CERFACS          |

# LLNL BG/P

| Site | System | Node Type | L1 Category | L2 Type | L3 Function            | Package           | Provider                  |

|------|--------|-----------|-------------|---------|------------------------|-------------------|---------------------------|

| LLNL | BG/P   | Service   | Prog Env    | Tool    | Infrastructure         | LaunchMON         | LLNL (Open Source)        |

| LLNL | BG/P   | Service   | Prog Env    | Tool    | Infrastructure         | MRNet             | University of Wisconsin   |

| LLNL | BG/P   | Service   | Prog Env    | Tool    | Infrastructure         | DynInst           | University of Wisconsin   |

| LLNL | BG/P   | Service   | Prog Env    | Tool    | Infrastructure         | StackWalker       | University of Wisconsin   |

| LLNL | BG/P   | Service   | Prog Env    | Tool    | Infrastructure         | secure VNC        | Vaporware                 |

| LLNL | BG/P   | Service   | Prog Env    | Tool    | GUI                    | Tool Gear         | LLNL(Open Source)         |

| LLNL | BG/P   | Service   | Prog Env    | Tool    | GUI                    | tcl/tk            | Open Source               |

| LLNL | BG/P   | Service   | Prog Env    | Tool    | GUI                    | X11               | Open Source               |

| LLNL | BG/P   | Service   | Prog Env    | Tool    | GUI                    | Qt                | TrollTech (Open Source)   |

| LLNL | BG/P   | Compute   | Prog Env    | Tool    | Performance Analysis   | Tau               | Paratools/Univ. of Oregon |

| LLNL | BG/P   | Compute   | Prog Env    | Tool    | Performance Analysis   | HPM               | Processor Vendor and Linu |

| LLNL | BG/P   | Compute   | Prog Env    | Tool    | Performance Analysis   | PAPI              | UTK(Open Source)          |

| LLNL | BG/P   | Compute   | Prog Env    | Tool    | Performance Analysis   | OTF               | Paratools (Open Source)   |

| LLNL | BG/P   | Service   | Prog Env    | Tool    | Performance Analysis   | Vampir/VampirServ | Dresden Univ              |

| LLNL | BG/P   | Service   | Prog Env    | Tool    | Performance Analysis   | VampirTrace       | Dresden Univ              |

| LLNL | BG/P   | Service   | Prog Env    | Tool    | Tool version selection | dotkit            | LLNL(Open Source)         |

| LLNL | BG/P   | Service   | Prog Env    | Tool    | Editor                 | emacs             | Open Source               |

| LLNL | BG/P   | Service   | Prog Env    | Tool    | Editor                 | vim               | Open Source               |

| LLNL | BG/P   | Compute   | Prog Env    | Tool    | Performance Analysis   | mpiP              | LLNL/ORNL(Open Source)    |

| LLNL | BG/P   | Service   | Prog Env    | Tool    | Source Code Control    | svn               | Open Source               |

| LLNL | BG/P   | Service   | Prog Env    | Tool    | Source Code Control    | cvs               | Open Source               |

| LLNL | BG/P   | Service   | Prog Env    | Tool    | Source Code Control    | git               | Open Source               |

# LLNL Viz/Analysis:

| Package            | Provider                        | Support     | Criticality |

|--------------------|---------------------------------|-------------|-------------|

| Vislt              | LLNL(Open Source)               | LLNL        | 1           |

| OpenGL             | Open Source                     | Community   | 1           |

| EnSight            | CEI                             | Licensing   | 2           |

| ImageMagick        | Open Source                     | Open Source | 2           |

| Tecplot            | Tecplot, Inc.                   | Licensing   | 2           |

| IDL                | ITT Visual Informations Systems | Licensing   | 2           |

| gnuplot            | Open Source                     | Open Source | 2           |

| POV-Ray            | Open Source                     | Community   | 2           |

| RasMol             | Open Source                     | Community   | 2           |

| vmd                | UIUC(Open Source)               | UIUC        | 2           |

| ParaView           | Open Source                     | Community   | 2           |

| NCAR               | NCAR(Open Source)               | NCAR        | 3           |

| mplayer            | Open Source                     | Community   | 3           |

| Blockbuster        | LLNL(Open Source)               | LLNL        | 3           |

| GIMP               | Open Source                     | Community   | 3           |

| xxdiff/tkdiff/meld | Open Source                     | Community   | 3           |

# Where We Are Today:

#### We are not prepared for the changes coming

- Hardware features are uncoordinated with software development

- (power mgmt, multicore tools, math libraries, advanced memory models, etc)

- Only basic acceptance test software is delivered with platform

- □ UPC, HPCToolkit, Optimized libraries, PAPI, can be YEARS late

- Vendors often "snapshot" key Open Source components and then deliver a stale code branch

- $\square$  Counterexample: A model that works MPICH for BG/P

- Community codes unprepared for sea change in architectures

- Coordination via SOW/contract is poor and only involves 2 parties

- No global evaluation of key missing components

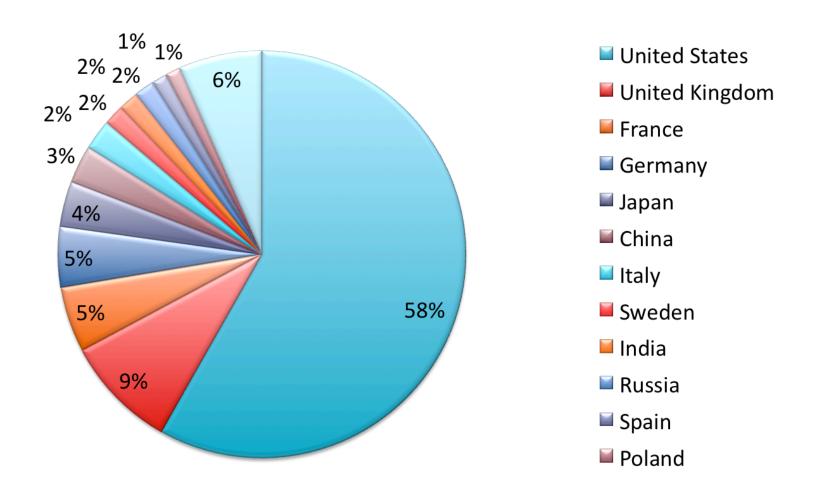

# International Community Effort

- International collaboration is required because:

- The scale of investment

- The need for international input on requirements

- Computational science projects are international

- Europeans, Japanese, and Americans are each working on portions of the software

- The process must be open

#### **Executive Committee:**

Co-Chair: Jack Dongarra, Univ, of Tennesse / ORNL, US

Co-Chair: Pete Beckman, Argonne National Laboratory, US

Franck Cappello, INRIA, FR

Thomas Lippert, Jülich Supercomputing Centre, DE

Satoshi Matsuoka, Tokyo Institute of Technology, JP

Paul Messina, Argonne National Laboratory, US

#### **An Example Development Community**

#### The Apache Software Foundation

Meritocracy in Action.

We consider ourselves not simply a group of projects sharing a server, but rather a community of developers and users.

| roject       | Sponsor             | A          | В    | C     | D                  | E     | F           | G                    | Н                  | I     | J         | KL    | М                  | N                  | 0            | Р            |               | Q     | R     | ns what, how elections take   | <ul> <li>HTTP Server</li> </ul>    | o FAQ                             |

|--------------|---------------------|------------|------|-------|--------------------|-------|-------------|----------------------|--------------------|-------|-----------|-------|--------------------|--------------------|--------------|--------------|---------------|-------|-------|-------------------------------|------------------------------------|-----------------------------------|

| uesky        | Incubator           | 2008-01-12 | 416  | True  | month              | False | True        | 2008-07-             | 22 224             | 0,0,8 | <b>7</b>  | 0 Tru | e Fa               | alse               | rue T        | rue T        | rue           | False | False | what's the philosophy behind  | o Abdera                           | <ul> <li>Licenses</li> </ul>      |

| ssandra      | Incubator           | 2009-01-01 | 61   | True  | month              | False | True        | 2009-01-             | 02 60              | 1,1,- | 9         | 0 Tru | e <u>Tr</u>        | ue I               | rue T        | <u>rue</u> F | alse          | False | False | nt. Come and see behind the   | <ul> <li>ActiveMQ</li> </ul>       | o News                            |

| lick         | Incubator           | 2008-07-21 | 225  | False | group-3            | True  | <u>True</u> | 2009-02-             | 22 9               | 2,3,4 | 7         | 0 Tru | e <u>Tr</u>        | ue I               | <u>rue</u> T | rue T        | <u>rue</u>    | True  | True  |                               | o Ant                              | <ul> <li>Public Reco</li> </ul>   |

| Composer     |                     | 2007-11-17 | 472  | False | group-3            | True  | <u>True</u> | 2008-10-             | 09 145             | 0,0,  | -         | 0 Tru | e Fa               | ilse 🛚             | <u>rue</u> T | rue T        | <u>rue</u>    | False | False |                               | o APR                              | <ul> <li>Sponsorship</li> </ul>   |

| roids        | HC,<br>Lucene       | 2008-10-09 | 145  | False | group-2            | True  | <u>True</u> | 2008-10-             | 23 131             | 0,0,3 | 4         | 0 Tru | e Tr               | <u>ue</u> ]        | rue T        | rue T        | <u> Frue</u>  | False | False |                               | o Archiva                          | o Donations                       |

| Empire-db    | Incubator           | 2008-07-08 | 238  | False | group-1            | True  | <u>True</u> | 2009-01-             | 05 <mark>57</mark> | 1,1,4 | 8         | 1 Tru | e Tn               | ue I               | <u>rue</u> T | rue T        | <u>rue</u>    | True  | True  |                               | o Beehive                          | o Thanks                          |

| ESME         | Incubator           | 2008-12-02 | 91   | True  | group-3            | True  | <u>True</u> | 2008-12-             | 05 88              | 0,1,- | <u>10</u> | 0 Tru | e Tn               | ue I               | <u>rue</u> T | rue T        | <u>rue</u>    | False | False |                               | o Camel                            | o Contact                         |

| Etch         |                     | 2008-09-02 | _    |       | group-3            | _     | True        | 2008-12-             |                    | 0,3,4 | _         | 0 Tru | e <u>Tr</u>        | ue I               | rue I        | rue T        | rue           |       | False |                               | o Cavenne                          |                                   |

| Hama         |                     | 2008-05-20 |      | _     | group-3            | _     | <u>True</u> | 2008-11-             |                    |       | _         | 0 Tru | e <u>Tr</u>        | ue I               | <u>rue</u> T | rue T        | <u>rue</u>    |       | False |                               |                                    | Farmalation De                    |

| mperius      |                     | 2007-11-10 | -    |       | group-1            | _     | True        | 2009-02-             |                    | 1,1,2 | _         | 1 Tru | e <u>Tr</u>        | ue I               | rue T        | rue T        | <u>rue</u>    |       | False |                               | o Cocoon                           | Foundation Pr                     |

| Security     |                     | 2008-05-20 | _    |       |                    | _     | <u>True</u> | 2008-09-             | _                  |       | _         | 0 Tru | <u>e</u> <u>Tr</u> | <u>ue</u> <u>1</u> | rue I        | rue I        | <u>rue</u>    |       | False |                               | o Commons                          | <ul> <li>Conference</li> </ul>    |

| ISPWiki      | Incubator<br>? not  | 2007-09-17 | 533  | False | group-1            | True  | <u>Irue</u> | 2008-09-             | 28 156             | 0,0,  | 12        | 1 Iru | e In               | ue l               | rue 1        | rue I        | rue           | False | False |                               | <ul> <li>Continuum</li> </ul>      | <ul> <li>Infrastructu</li> </ul>  |

| Cato         | ? not<br>known      |            | ?    | True  | group-3            | True  | False       |                      | ?                  |       | 9         | 0 Tru | e <u>Tn</u>        | ue I               | rue T        | rue T        | <u>rue</u>    | False | False |                               | o CouchDB                          | o JCP                             |

| og4php       | Logging<br>Services | 2004-01-31 | 1858 | False | group-3            | True  | <u>True</u> | 2007-07-             | 18 594             | 0,0,0 | 6         | 0 Tru | e Tr               | ue I               | rue I        | rue T        | <u> rue</u>   | False | False |                               | o CXF                              | <ul> <li>Legal Affairs</li> </ul> |

| okahi        | Incubator           | 2006-03-01 | 1098 | False | group-2            | True  | True        | 2006-11-             | 28 826             | 0,0,0 | 5         | 0 Tru | e Tr               | ue I               | rue T        | rue T        | <u>rue</u>    | False | False |                               | o DB                               | <ul> <li>Security</li> </ul>      |

| ucene.Net    | Lucene              | 2006-03-15 | 1084 | False | group-1            | True  | True        | 2006-11-             | 11 843             | 0,0,0 | 4         | 1 Tru | e Tr               | ue I               | rue T        | rue T        | <u>rue</u>    | False | False |                               | <ul> <li>Directory</li> </ul>      | <ul> <li>Travel Assis</li> </ul>  |

| Olio         | Incubator           | 2008-09-29 | 155  | False | group-1            | True  | <u>True</u> | 2009-02-             | 05 <mark>26</mark> | 1,3,5 | 12        | 0 Tru | e <u>Tn</u>        | ue I               | rue T        | rue T        | <u>rue</u>    | True  | False |                               | o Excalibur                        |                                   |

| OpenWebBeans | Incubator           | 2008-10-26 | 128  | False | group-3            | True  | <u>True</u> | 2009-01-             | 18 44              | 1,7,7 | 6         | 2 Tru | e Tn               | ue T               | <u>rue</u> T | rue T        | <u>rue</u>    | True  | True  |                               | o Felix                            | How it works                      |

| PDFBox       |                     | 2008-02-07 |      |       | group-2            |       | <u>True</u> | 2009-01-             |                    | 3,3,3 |           | 2 Tru | e <u>Tr</u>        | ue I               | rue I        | rue I        | <u>rue</u>    |       | False | n incorporated in the United  | o Forrest                          | o Introduction                    |

| PhotArk      |                     | 2008-08-19 |      |       | group-2            | _     | True        | 2008-10-             | _                  |       |           | 0 Tru | e <u>Tr</u>        | ue I               | rue I        | rue T        | rue           | False |       | in incorporated in the chiled | o Geronimo                         | Meritocracy                       |

| Pivot        |                     | 2009-01-26 | _    |       | group-2            |       | <u>True</u> | 2009-02-             | _                  | 1,-,- | _         | 0 Fal | se <u>Tr</u>       | ue I               | rue T        | rue T        | $\overline{}$ |       | False |                               |                                    |                                   |

| RAT          |                     | 2008-01-06 |      |       | group-3            | _     | True        | 2009-02-             | _                  | 3,3,3 | _         | 0 Tru | <u>e</u> <u>Tr</u> | <u>ue</u> ]        | rue I        | rue I        | _             |       | False |                               | o Gump                             | <ul> <li>Structure</li> </ul>     |

| RCF          |                     | 2007-04-06 |      |       | group-1            | _     | True        | 2008-04-<br>2008-11- |                    | 0,0,0 | _         | O Tru | <u>e In</u>        | ue I               | rue I        | rue F        | alse          | False | False | ects by supplying hardware,   | <ul> <li>Hadoop</li> </ul>         | o Roles                           |

| Sanselan     |                     | 2006-12-26 |      |       | group-3<br>group-1 | _     | True        | 2008-11-             |                    |       | _         | 0 1   | o Tr               | ue I               | ruo T        | ruo T        | rue           | True  | True  |                               | <ul> <li>Harmony</li> </ul>        | <ul> <li>Collaboration</li> </ul> |

| anatian      | incubator           | 2007-03-03 | 341  |       |                    |       | aepe        |                      |                    |       |           | wnic  | cn c               | omr                | anie         | s ar         | na ir         | nalvi | duais | can donate resources and be   | <ul> <li>HiveMind</li> </ul>       | <ul> <li>Infrastructu</li> </ul>  |

|              |                     |            |      |       |                    |       |             | resour               | -                  |       |           |       |                    |                    |              |              |               |       |       |                               | <ul> <li>HttpComponents</li> </ul> | <ul> <li>Incubator</li> </ul>     |

## **Apache Foundation**

- Create a foundation for open, collaborative software development projects by supplying hardware, communication, and business infrastructure

- Incubator projects can become Apache projects

- 800 "committers"

- The ASF Infrastructure is mostly composed of the following services:

- the web serving environment (web sites and wikis)

- the code repositories

- the mail management environment

- the issue/ bug tracking

- the distribution mirroring system

#### A Plan Could Include:

- Work with vendors to create the HPC equivalent to the ITRS (Int'l Tech Roadmap for Semiconductors)

- Get community working on software before machine becomes available

- Community proposed unified roadmap for exascale software

- Identify missing components for future architectures and a plan to address them

- Develop models for working more closely with vendors

- (support, acceptance tests, target features)

- Identify key application areas to drive development

- Community software development models

- Funding and organizational models (Apache, etc)

#### Achievable Outcomes

- Improve the capability of computational science

- Build and strengthen international collaborations and leadership; deliver more capable, productive HPC systems

- Build and improve R&D program developing new programming models and tools addressing extreme scale

- Strategic plan for HPC research

- Open source HPC development guided by roadmap with better coordination and fewer missing components

- Joint programs in education and training for the next generation of computational scientists.

- Vendor engagement and coordination for more capable software supporting exascale science

# Possible Models (from loose to tight collaboration)

- Identify needs, focus Int'l R&D attention on missing components

- Coordinate features, delivery schedule, interoperability, and improvements across international R&D teams

- IESP community recommends funding for key areas

- Provide forums for vendors and community to work together on roadmaps

- Fund R&D and subsequent deployment of key components

- Fund collaborative relationship with vendors and co-develop components

- □ Test, integrate, and support internationally developed software components

- Build integrated software that can pass acceptance tests on extreme platforms

# Future Workshops and Report

- 3 workshops over the next year

- □ 1: Santa Fe, April 7-8

- 2: France, June 28-29

- 3: Japan in the early Fall

- Broad engagement by the community

- Initial reports in summer 2009

- Final report for first year at SC09

- Planning for IMMEDIATE payoff

- Could begin initial components of plan this year

## www.exascale.org

HOME MEETINGS DOCUMENTS COMMUNITY

MAIN PAGE

DISCUSSION

VIEW SOURCE

HISTORY

The mission of the International Exascale Software

Project (IESP) is to lay the foundation for exascale

computing by mobilizing the global open source software

community to combine and coordinate their collective

efforts far more efficiently and effectively than ever

before. The IESP will hold a series of three workshops to

organize and structure this community wide effort. The

first, invitation-only workshop will occur on April 7th and

8th in Sante Fe, New Mexico, US, with people arriving in

time for a reception on April 6th. Attendees will include

#### WORKSHOP INFORMATION

Workshop Arrangements

Workshop Agenda

Workshop Charge

Executive Committee

Organizing Committee

Workshop Attendees

Whitepapers

Background Material

members from industry, academia, and government, with expertise in a range of critical areas.

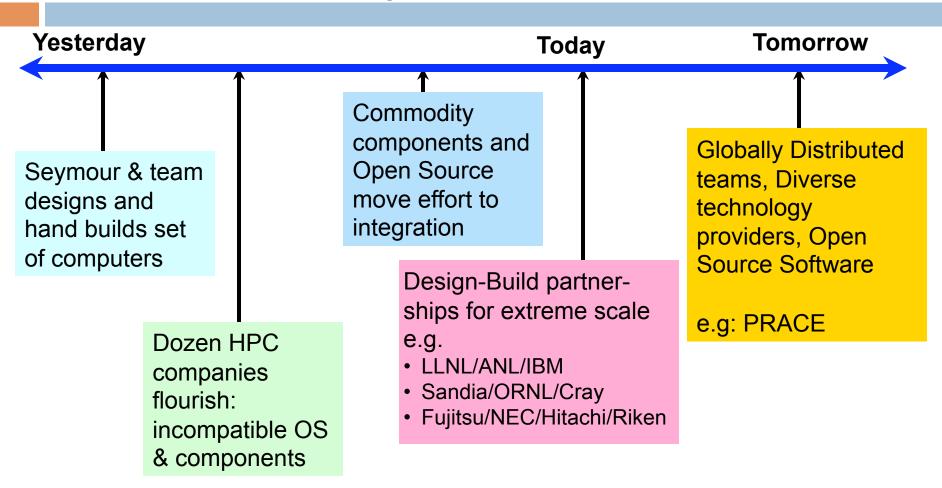

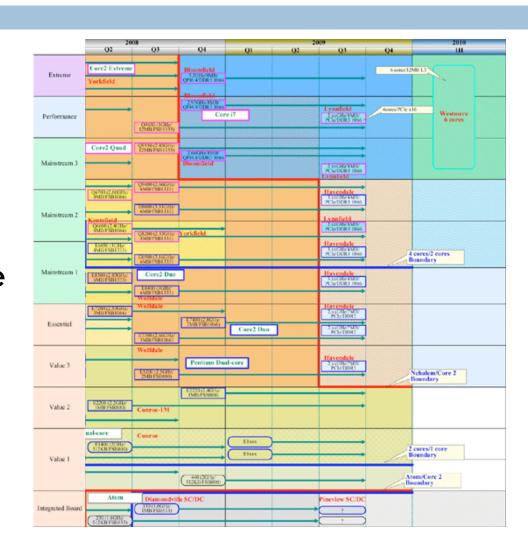

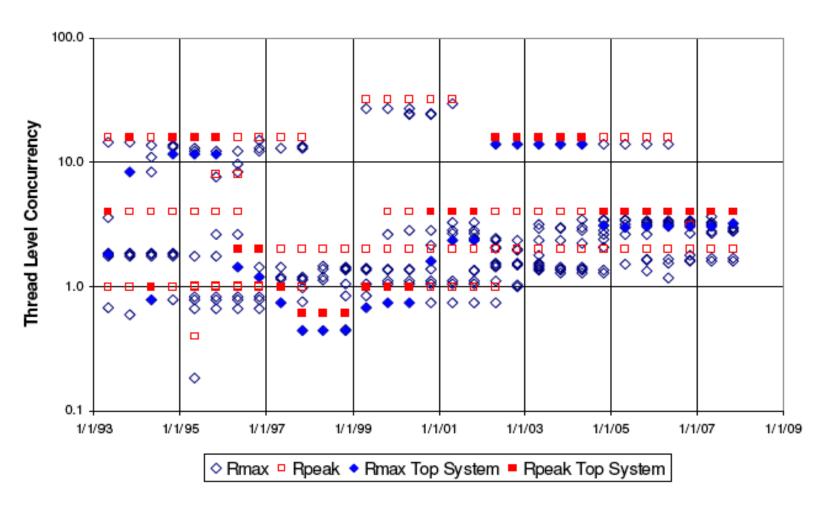

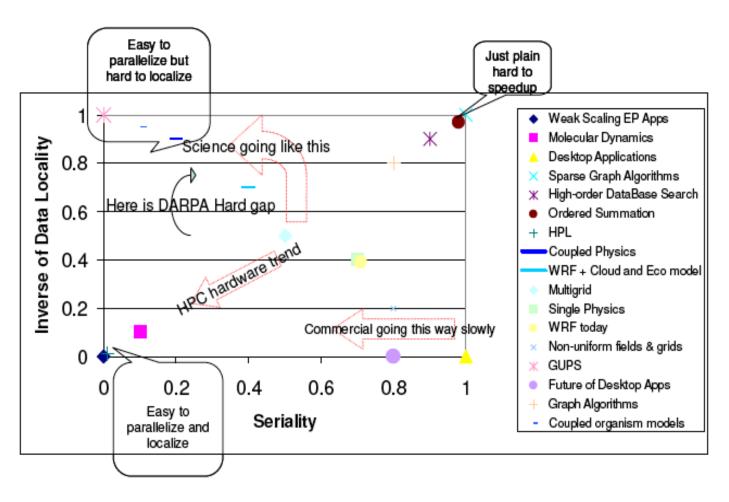

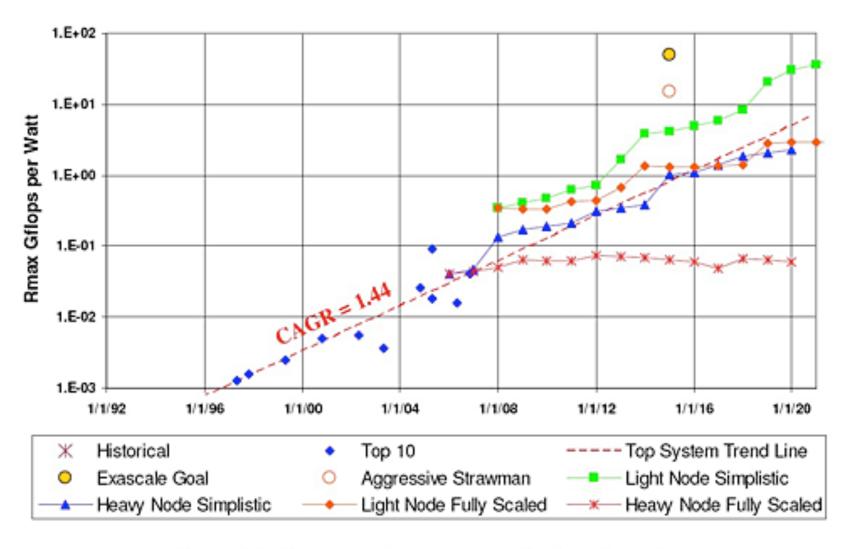

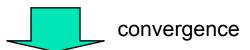

# Thou Shalt Specialize or Commoditize? The Japanese Situation Towards Peta and Exascale

Satoshi Matsuoka, Prof., Dr. Sci.

GSIC Center, Tokyo Institute of Technology / National Institute of Informatics

DoE IESP Workshop @ Santa Fe, NM, USA Apr. 6-8, 2009

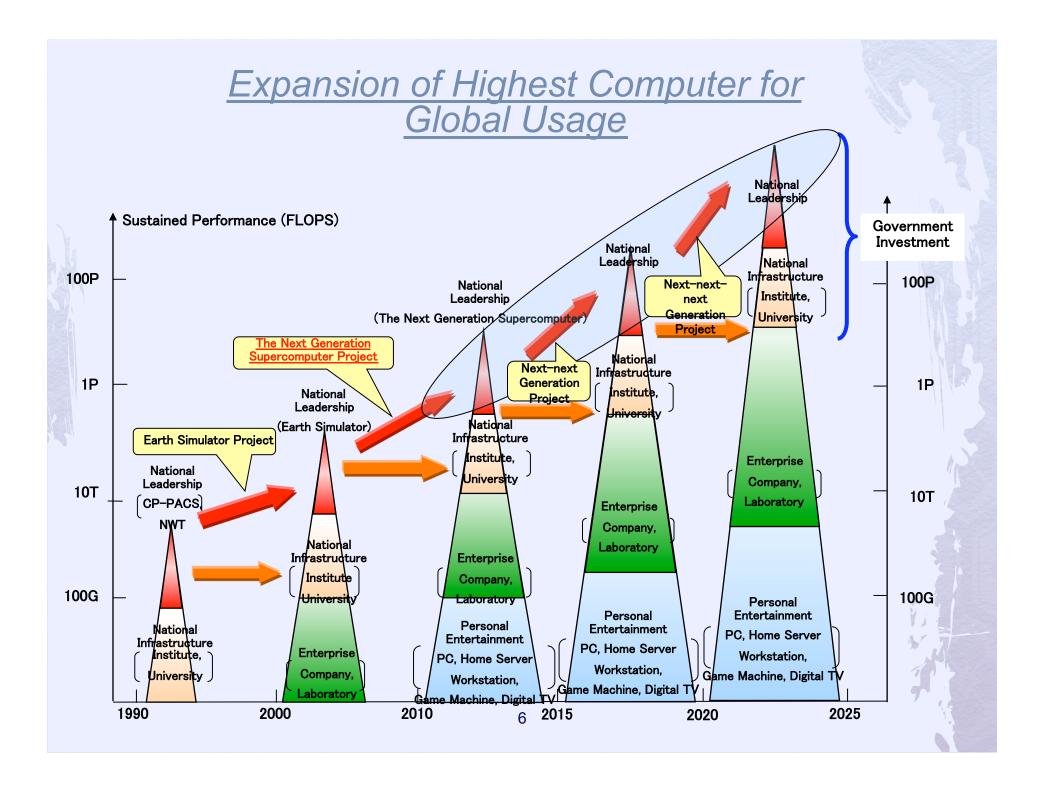

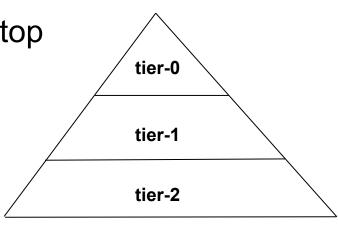

# The Ideal: Hiearchy of Deployments

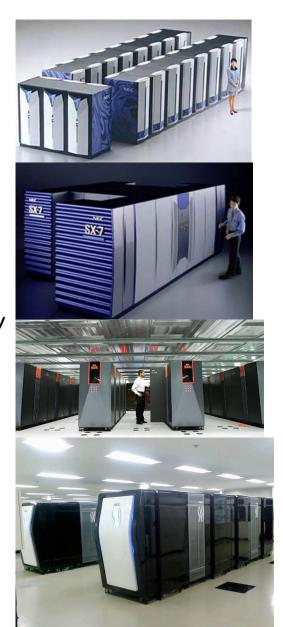

# Vector Machines- NEC SX

- ACOS/SX-1

- SX-2 (1983): Bipolar, 4-wide,

1.3GFlops, single CPU

- SX-3: (1989): Bipolar, 8-wide, 22GFLOPS(2x4CPUs)

- SX-4 (1994): CMOS 8-wide 64GF/ node (2GF x 32CPUs)

- SX-5 (1998): 16wide, 128GF/node (8GF x 16 CPUs)

- SX-6 (2001): 8-wide x 2 clock, 64GF/ node (8x8CPUs), core of ES

- SX-7 (2002): 8-wide x 2 clock, 282GF/node (9GF x 32 CPUs)

- SX-8 (2004): 8-wide 2Ghz vector,

128GF/node (16GF x 8CPUs)

- 5X-9 (2007): 8-wide x 4 3.2 Ghz 102GF/CPU, 1.6TF/node, 128GB/s inter-node BW

# Glory Days of Vectors...just 12 years ago

| Cray        | 71  |      |

|-------------|-----|------|

| NEĆ         | 40  |      |

| Fujitsu     | 33  | (#2` |

| Hitachi     | 9   | ,    |

| CM-2        | 7   |      |

| Total       | 160 |      |

|             |     |      |

| x86 (Meiko) | 3   |      |

#### "Cretaceous

TOP500 Sublist Generator

$R_{max}$  and  $R_{peak}$  values are in GFlops. For more details about other fields, check the TOP500 description.

Top500 June 1996, 40 NEC SXs

| Rank | Site                                                    | System          | Cores | R <sub>max</sub> | Rpeak |

|------|---------------------------------------------------------|-----------------|-------|------------------|-------|

| 10   | HWW/Universitaet Stuttgart<br>Germany                   | SX-4/32<br>NEC  | 32    | 66.53            | 64    |

| 11   | NEC Fuchu Plant<br>Japan                                | SX-4/32<br>NEC  | 32    | 66.53            | 64    |

| 24   | Japan Marine Science and Technology<br>Japan            | SX-4/20<br>NEC  | 20    | 42.4             | 40    |

| 25   | National Research Institute for Metals<br>Japan         | SX-4/20<br>NEC  | 20    | 42.4             | 40    |

| 26   | Toyota Central Research & Development Japan             | SX-4/20<br>NEC  | 20    | 42.4             | 40    |

| 30   | National Aerospace Laboratory (NLR)<br>Netherlands      | SX-4/16<br>NEC  | 16    | 34.42            | 32    |

| 31   | National Cardiovascular Center<br>Japan                 | SX-4/16<br>NEC  | 16    | 34.42            | 32    |

| 41   | Swiss Scientific Computing Center (CSCS)<br>Switzerland | SX-4/12<br>NEC  | 12    | 25.8             | 24    |

| 49   | Atmospheric Environment Service (AES) Canada            | SX-3/44R<br>NEC | 4     | 23.2             | 25.6  |

| 50   | Tohoku University<br>Japan                              | SX-3/44R<br>NEC | 4     | 23.2             | 25.6  |

| 55   | Atmospheric Environment Service (AES) Canada            | SX-3/44<br>NEC  | 4     | 20               | 22    |

| 59   | Institute for Molecular Science Japan                   | SX-3/34R<br>NEC | 3     | 17.4             | 19.2  |

| 60   | ATR Optical Communication Lab<br>Japan                  | SX-4/8<br>NEC   | 8     | 17.2             | 16    |

| 61   | Atmospheric Environment Service (AES) Canada            | SX-4/8<br>NEC   | 8     | 17.2             | 16    |

| 62   | Danish Meteorological Institute<br>Denmark              | SX-4/8<br>NEC   | 8     | 17.2             | 16    |

| 63   | National Geographic Agency<br>Japan                     | SX-4/8<br>NEC   | 8     | 17.2             | 16    |

| 111  | Veritas DGC<br>United States                            | SX-4/6<br>NEC   | 6     | 12.9             | 12    |

| 136  | German Aerospace Laboratory (DLR)<br>Germany            | SX-3/24R<br>NEC | 2     | 11.6             | 12.8  |

| 137  | National Institute for Fusion Science Japan             | SX-3/24R<br>NEC | 2     | 11.6             | 12.8  |

Japan had ~30% performance share as a country

#### Rise of the Commodity Clusters: "The Scenario"

High Performance Commodity Computing

- -High Performance x86 CPUs

- -Fast Commodity Interconnect

- -Cluster Software

Myrinet, Infiniband, etc.

Rise and spread of Commodity Clusters and increase in their size

Real-time tracking of technology curve

SC Technology Curve

Operation

Design Cluster Complete

Start Decommi Operation

Tradtional SCs

Time

Widespread Use of Clusters:

Small to very large (e.g.

TSUBAME, Ranger)

# The First Beowulf - Wiglaf (1993~4) (NASA/CalTech)

- 16 processors

- Intel 80486 100 MHz

- VESA Local bus

- 256 Mbytes memory

- 6.4 Gbytes of disk

- Dual 10 base-T Ethernet

- 72 Mflops sustained, on real PPM code

- \$40K

- · Did not even come close

# Early PC Clusters & Top500

- The 1<sup>st</sup> WS Cluster ranked: June 1997 (The 9<sup>th</sup> Top500)

- UC Berkeley NOW, 344th (10.14 GFlops)

- The 1<sup>st</sup> PC Cluster ranked: June 1999 (The 13<sup>th</sup> Top500)

- Univ. Bonn, Parnass2 Cluster, 362nd (29.5 GFlops)

- The 1<sup>st</sup> US PC Cluster: June 2000 (The 15<sup>th</sup> Top500)

- NCSA (Windows) NT Supercluster, 207th (62 GFlops)

- The 1<sup>st</sup> Teraflop Cluster: Nov. 2002 (The 19<sup>th</sup> Top500)

- LLNL MCR Linux Networx Linux Cluster Xeon 2.4 GHz Quadrics, 5<sup>th</sup> (5694 Gflops)

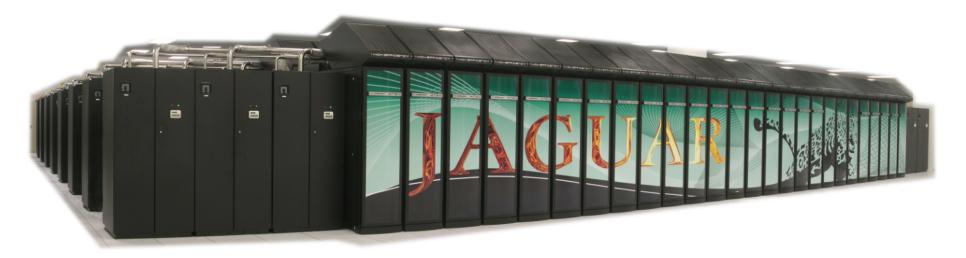

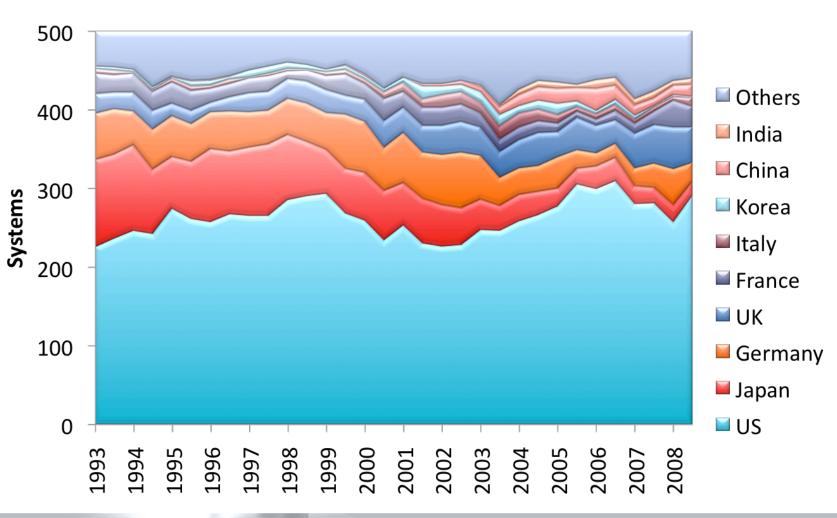

# And this went to Petascale, Despite all the Skepticism

- TACC Ranger

- The largest x86 Linux Cluster ~50,000 x86 cores

- 4<sup>th</sup> (326 TFlops) June 2008 (The 30th Top500)

- RR: the first #1 "commodity" cluster on Top500 June 2008(The 30th Top500)

- The first Petaflop machine

- The first #1 machine to use IB

- The first #1 Linux machine

- The first #1 "heterogeneous" SC (Cell and Opteron)

## From Computonik Shock to

Apollomodity Shock

2002 The Japanese Computnik article here

- 2002 The Japanese Earth Simulator New York Times "Computonik Shock"

- Top500 #1 @ 35.8 TeraFlops

- 2004-5 US BG/L >100Tera like the Geminis

- 2008 US Roadrunner hitting Peta like Apollo 11 "commodity prevails"

The world's fastest computer uses chips based on one from Sony's PlayStation 3.

wrong," said Michael R. Anastasio, a physicist who is director of the Los Alamos National Laboratory. "This gives us a window into a whole new way of computing. We can look at phenomena we have never seen before." reclaimed the speed record for the United States. The Japanese challenge, however, led Congress and the Bush administration to reinvest in high-performance computing.

"It's a sign that we are maintaining our position," said Peter J. Ungaro, chief executive of Cray, a maker of supercomputers. He noted, however, that "the real competitiveness is based on the discoveries that are based on the machines."

Having surpassed the petaflop barrier, I.B.M. is already looking toward the next generation of supercomputing. "You do these

"One small step for RR, one giant leap for supercomputing"

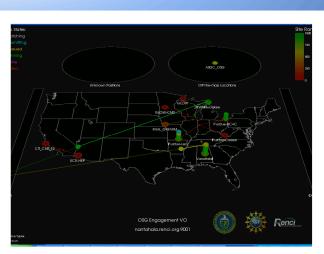

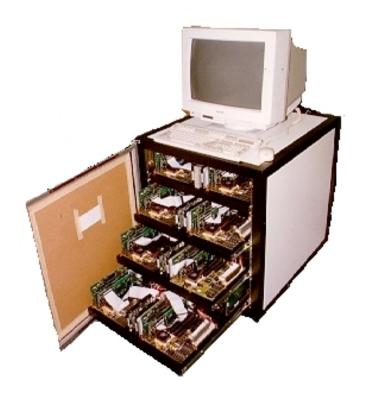

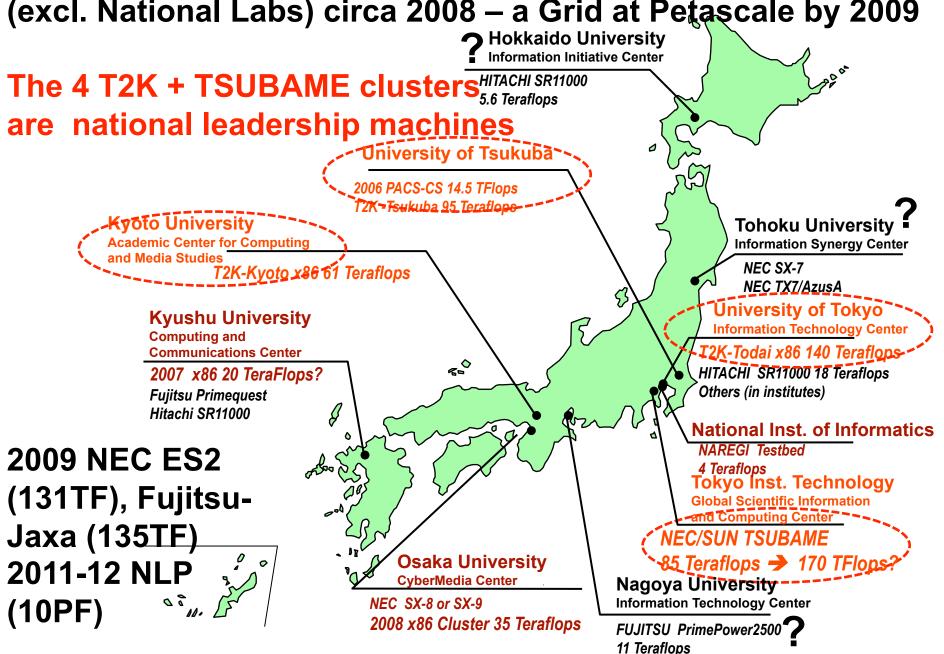

Japan's 9 Major University Computer Centers (excl. National Labs) circa 2008 – a Grid at Petascale by 2009

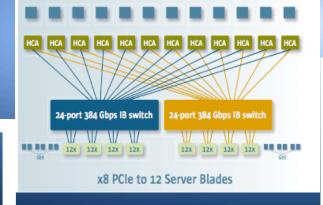

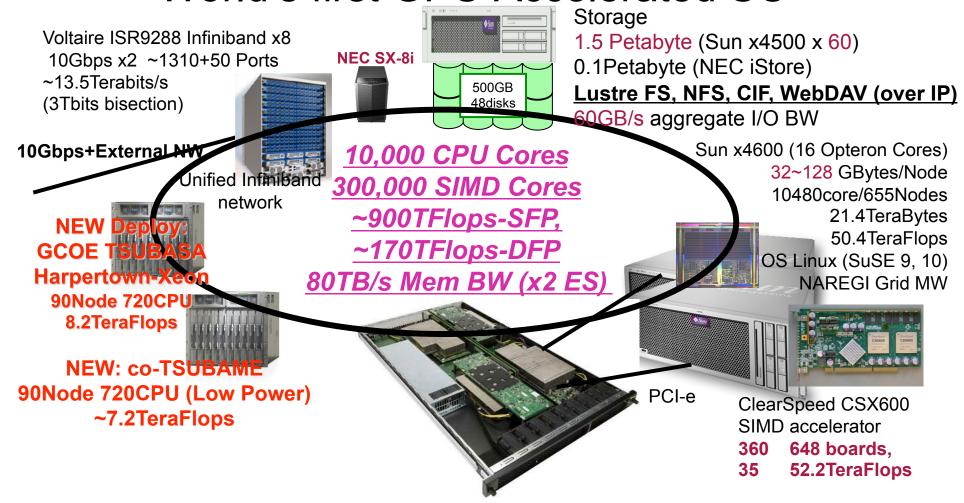

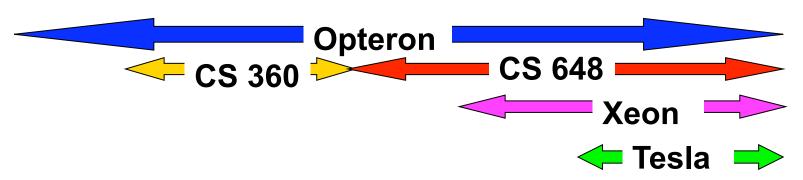

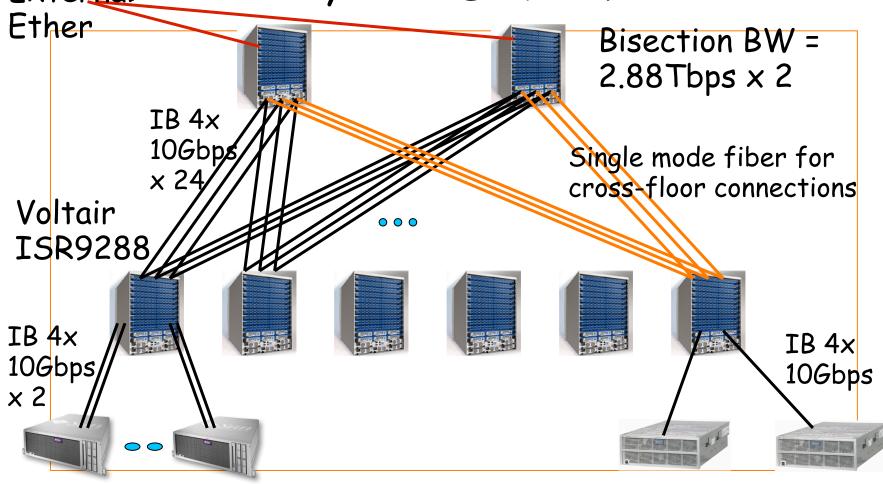

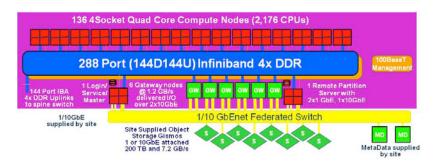

### The TSUBAME 1.0 @ Tokyo Tech. Spring 2006-- ~80 Teraflops Peak Unified IB network

Voltaire ISR9288 Infiniband 10Gbps x2 (DDR next ver.)

~1310+50 Ports

~13.5Terabits/s (3Tbits bisection)

10Gbpe+External Network

*"Fastest*

Supercomputer in

Asia" 7th on the 27th

*Top500@38.18TF* OS inux (SuSE 9, 10)

Sun Galaxy 4 (Opteron Dual

core 8-socket)

10480core/655Nodes

21.4Terabytes

50.4TeraFlops

NAREGI Grid MW

Storage

1.0 Petabyte (Sun "Thumper")

0.1Petabyte (NEC iStore)

Lustre FS, NFS, WebDAV (over IP)

50GB/s aggregate I/O BW

ClearSpeed CSX600 SIMD accelerator

360 boards.

35TeraFlops(Current))

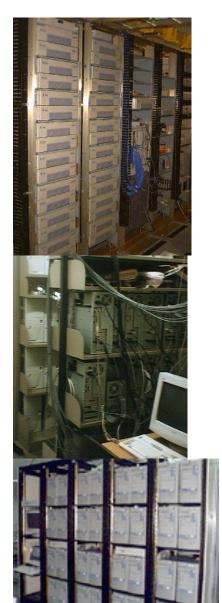

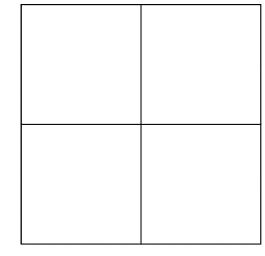

### T2K Open Supercomputer Alliance

- Primary aiming at design of common Open hardware architecture with specification of new supercomputers.commodity devices & technologies.

- Now extending to collaborative work Open software stack with openon research, education, grid operation, our ce middleware & tools. ..., for inter-disciplinary computation al Open to user's needs not only in FP & HPC field but also INT world. (& computer) science.

#### **Kyoto Univ**

416 nodes (61.2TF) / 13TB

**Linpack Result:**

Rmax = 50.5TF

#### Univ. Tokyo

952 nodes (140.1TF) / 31TB **Linpack Result:**

Rmax = 83.0TF

#### Univ. Tsukuba

648 nodes (95.4TF) / 20TB

**Linpack Result:**

Rpeak = 61.2TF (416 nodes) Rpeak = 113.1TF (512+256 nodes)Rpeak = 92.0TF (625 nodes)

Rmax = 76.5TF

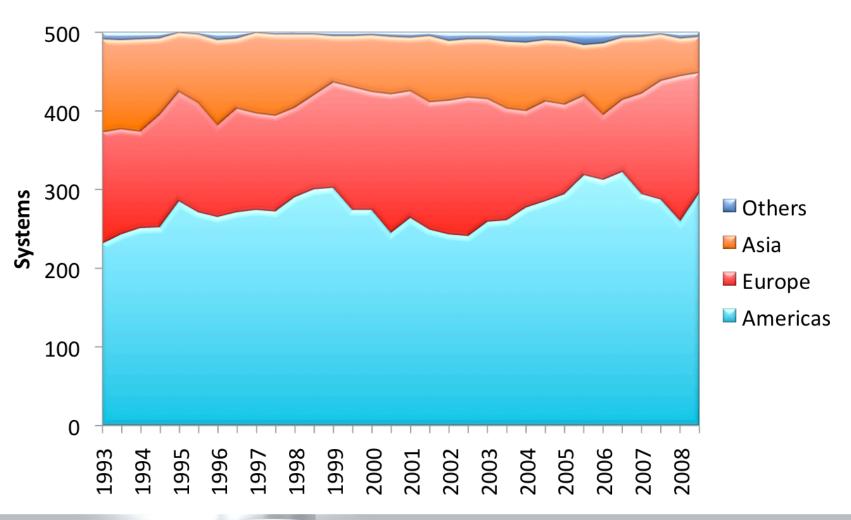

### From Glory Days to Near Extinction...in 10+ years

- Japan as a country now only has 4% share --- now beaten by France

- Big Iron Vector & SMP SC now "niche"

- Clusters too small for cost, vendor inexperiences

"Cretaceous"

"Paleogene"

(Top500 Jun 2008 --- just 1 SX)

#### **TOP500 Sublist Generator**

R<sub>max</sub> and R<sub>peak</sub> values are in GFlops. For more details about other fields, check the

### Top500 June 1996, 40 NEC SXs

| Rank | Site                                                    | System          | Cores | Rmax  | Rpeak |

|------|---------------------------------------------------------|-----------------|-------|-------|-------|

| 10   | HWW/Universitaet Stuttgart<br>Germany                   | SX-4/32<br>NEC  | 32    | 66.53 | 64    |

| 11   | NEC Fuchu Plant<br>Japan                                | SX-4/32<br>NEC  | 32    | 66.53 | 64    |

| 24   | Japan Marine Science and Technology<br>Japan            | SX-4/20<br>NEC  | 20    | 42.4  | 40    |

| 25   | National Research Institute for Metals<br>Japan         | SX-4/20<br>NEC  | 20    | 42.4  | 40    |

| 26   | Toyota Central Research & Development Japan             | SX-4/20<br>NEC  | 20    | 42.4  | 40    |

| 30   | National Aerospace Laboratory (NLR)<br>Netherlands      | SX-4/16<br>NEC  | 16    | 34.42 | 32    |

| 31   | National Cardiovascular Center<br>Japan                 | SX-4/16<br>NEC  | 16    | 34.42 | 32    |

| 41   | Swiss Scientific Computing Center (CSCS)<br>Switzerland | SX-4/12<br>NEC  | 12    | 25.8  | 24    |

| 49   | Atmospheric Environment Service (AES) Canada            | SX-3/44R<br>NEC | 4     | 23.2  | 25.6  |

| 50   | Tohoku University<br>Japan                              | SX-3/44R<br>NEC | 4     | 23.2  | 25.6  |

| 55   | Atmospheric Environment Service (AES) Canada            | SX-3/44<br>NEC  | 4     | 20    | 22    |

| 59   | Institute for Molecular Science<br>Japan                | SX-3/34R<br>NEC | 3     | 17.4  | 19.2  |

| 60   | ATR Optical Communication Lab<br>Japan                  | SX-4/8<br>NEC   | 8     | 17.2  | 16    |

| 61   | Atmospheric Environment Service (AES) Canada            | SX-4/8<br>NEC   | 8     | 17.2  | 16    |

| 62   | Danish Meteorological Institute<br>Denmark              | SX-4/8<br>NEC   | 8     | 17.2  | 16    |

| 63   | National Geographic Agency<br>Japan                     | SX-4/8<br>NEC   | 8     | 17.2  | 16    |

| 111  | Veritas DGC<br>United States                            | SX-4/6<br>NEC   | 6     | 12.9  | 12    |

| 136  | German Aerospace Laboratory (DLR)<br>Germany            | SX-3/24R<br>NEC | 2     | 11.6  | 12.8  |

| 137  | National Institute for Fusion Science<br>Japan          | SX-3/24R<br>NEC | 2     | 11.6  | 12.8  |

2008/06/24 16:29:29 cs Sublist Generate

### R<sub>max</sub> and R<sub>peak</sub> v luQai 0 5000 md e co a/out 2e010 cleck the 2p5 N EE C SXS

2 entries found.

| Rank | Site                                  | System                 | Cores | R <sub>max</sub> | R <sub>peak</sub> |

|------|---------------------------------------|------------------------|-------|------------------|-------------------|

| 30   | The Earth Simulator Center<br>Japan   | Earth-Simulator<br>NEC | 5120  | 35.86            | 40.96             |

| 200  | HWW/Universitaet Stuttgart<br>Germany | SX8/576M72<br>NEC      | 576   | 8.92             | 9.22              |

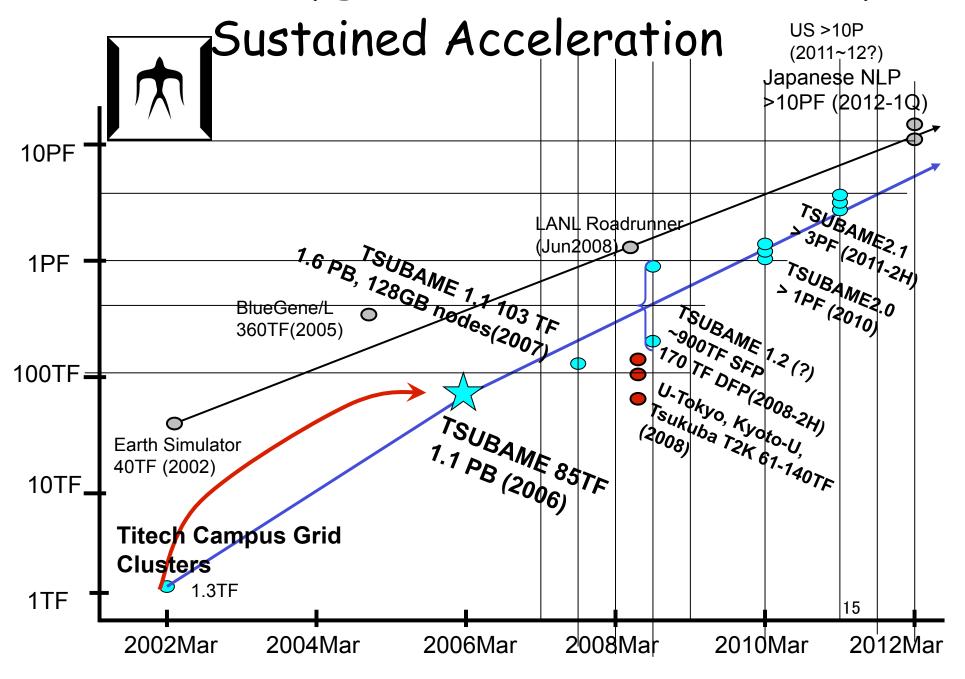

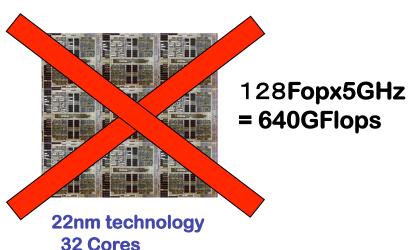

### In Response: Japanese Petascales

- The Next Leadership Petascale machine

- > 10 Petaflops

- Specialized

- ½ NEC Vector, ½ Fujitsu SPARC derivative

- Huge, Expensive (\$1 bill)

Vs.

- Commodity efforts e.g. TSUBAME 2.0, T2K follow ons

- The ES vs. TSUBAME 1.0 battle

- The ES2 & Jaxa Fujitsu vs. T2K&TSUBAME 1.2

- NLP vs. Gen 2 T2K& TSUBAME2.0?

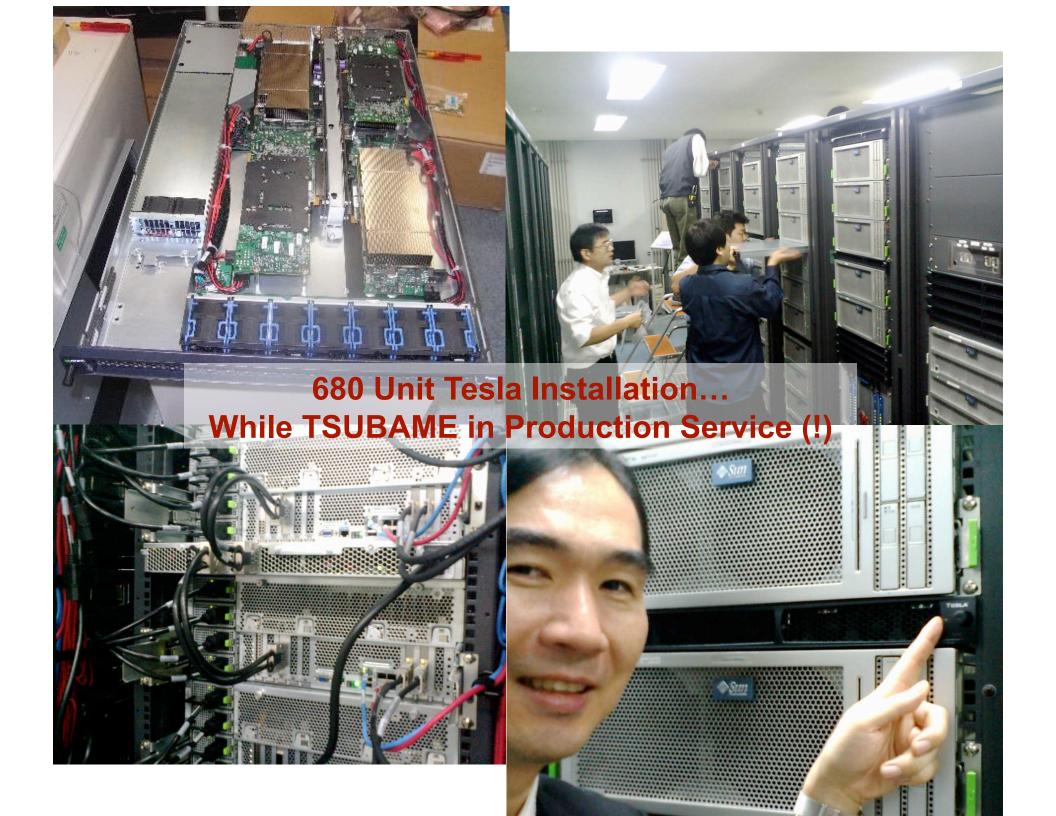

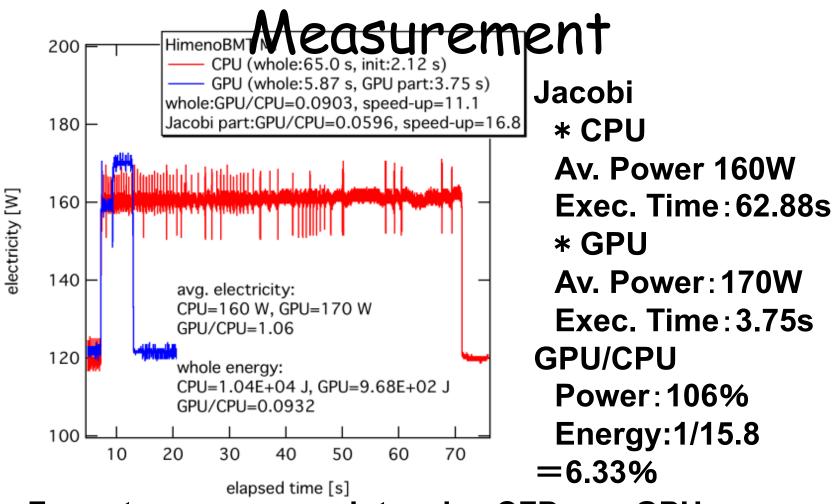

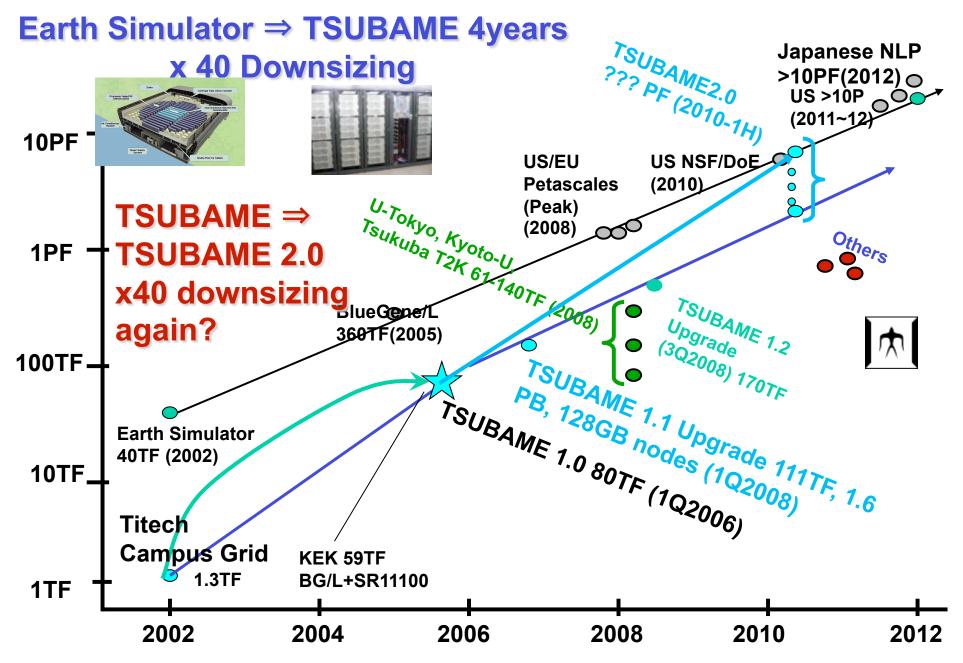

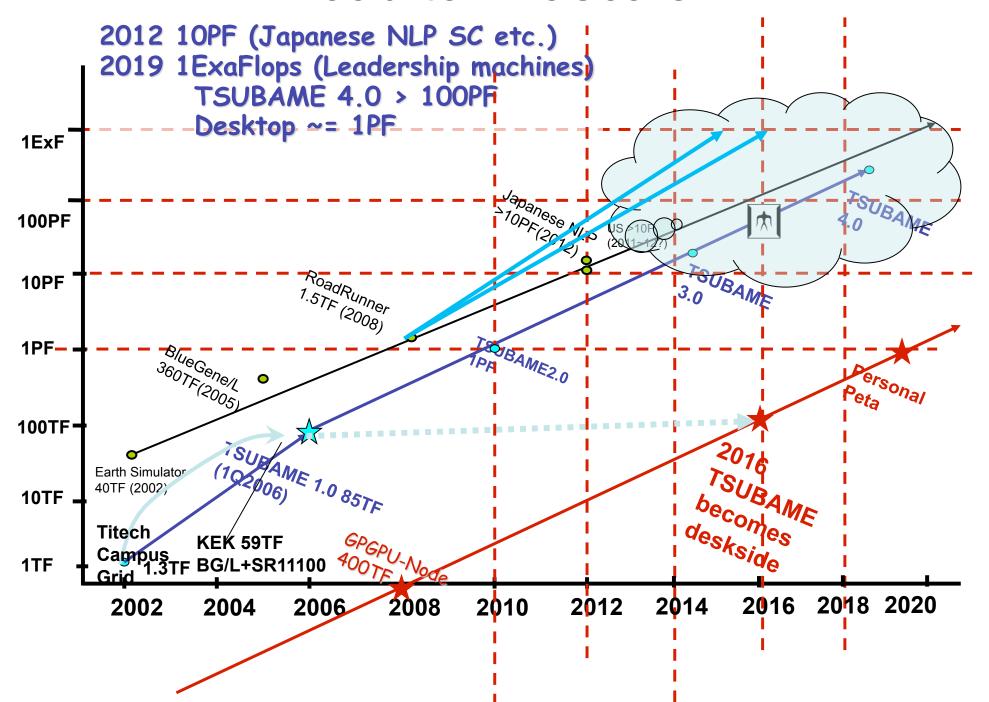

### TSUBAME Upgrades Towards Petaflops

### Biggest Problem is Power...

| Machine                     | CPU Cores | Watts     | Peak<br>GFLOPS | Peak<br>MFLOPS/<br>Watt | Watts/<br>CPU<br>Core | Ratio c.f.<br>TSUBAME |

|-----------------------------|-----------|-----------|----------------|-------------------------|-----------------------|-----------------------|

| TSUBAME(Opteron)            | 10480     | 800,000   | 50,400         | 63.00                   | 76.34                 |                       |

| TSUBAME2006 (w/360CSs)      | 11,200    | 810,000   | 79,430         | 98.06                   | 72.32                 |                       |